ISO9001:2015 质量管理体系受控文件

## TX8W7010 用户手册

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2023-02-03 |               | 文件版本 | V1.7                |

## 修订记录

| 日期         | 版本   | 描述                                                                                                                                           | 修订人 |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2023-02-03 | V1.7 | 1、解决部分设备打开阅读时，出现乱码问题                                                                                                                         | YLC |

| 2023-01-09 | V1.6 | 1、修改 CMP_STA[5:2]的寄存器错误描述。补充对 CMP_STA[7:6]的描述。修改 CMPO_CON4[4], CMPO_CON4[6], CMP1_CON4[4], CMP1_CON4[6]的描述使之更容易理解。修改低功耗管理章节的关于进入 IDLE 模式的描述； | YLC |

| 2022-08-10 | V1.5 | 1、修改 ADC 模块的分频比描述                                                                                                                            | TX  |

| 2022-03-18 | V1.4 | 1、修改 AIP_CON1 寄存器第 1 和 0 位的错误描述。修改模拟比较器 CON4 的 N 管 P 管开关功能的描述。                                                                               | TX  |

| 2022-03-10 | V1.3 | 1、完善 RF 收发器 2.4G 模式用户使用说明。                                                                                                                   | TX  |

| 2022-03-09 | V1.2 | 1、完善 RF 收发器 2.4G 模式用户使用说明。                                                                                                                   | TX  |

| 2022-03-03 | V1.1 | 1、补充 RF 收发器用户寄存器使用说明。                                                                                                                        | TX  |

| 2022-03-03 | V1.0 | 1、初始版本                                                                                                                                       | TX  |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

## 目录

|                                  |    |

|----------------------------------|----|

| TX8W7010 用户手册 .....              | 1  |

| 1. 产品概述 .....                    | 1  |

| 1. 1. 说明 .....                   | 1  |

| 1. 2. 特性 .....                   | 2  |

| 1. 3. 引脚分配 .....                 | 5  |

| 1. 4. 封装信息 .....                 | 5  |

| 1. 5. 封装尺寸图 .....                | 5  |

| 1. 6. 引脚说明 .....                 | 6  |

| 2. 中央处理器 .....                   | 8  |

| 2. 1. 累加器（ACC） .....             | 8  |

| 2. 2. 寄存器（B） .....               | 9  |

| 2. 3. 堆栈指针寄存器（SP） .....          | 9  |

| 2. 4. 堆栈指针寄存器（SPH） .....         | 9  |

| 2. 5. 数据指针寄存器（DPTR0/DPTR1） ..... | 10 |

| 2. 6. 数据指针控制寄存器（DPCFG） .....     | 10 |

| 2. 7. 程序状态寄存器（PSW） .....         | 12 |

| 2. 8. 程序计数器（PC） .....            | 12 |

| 3. 存储器 .....                     | 13 |

| 3. 1. 程序存储器 .....                | 13 |

| 3. 2. XDATA .....                | 14 |

| 3. 3. IDATA .....                | 15 |

| 3. 4. SFR 空间 .....               | 17 |

| 4. 系统时钟 .....                    | 18 |

| 4. 1. 时钟系统概述 .....               | 18 |

| 4. 2. 时钟系统主要功能 .....             | 18 |

| 4. 3. 时钟系统框图 .....               | 19 |

| 4. 4. 系统振荡器 .....                | 20 |

| 4. 4. 1. 内部低速 RC 振荡器 .....       | 20 |

| 4. 4. 2. 内部高速 RC 振荡器 .....       | 20 |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                            |    |

|----------------------------|----|

| 4. 4. 3. 外部低速晶体振荡器 .....   | 20 |

| 5. 复位系统 .....              | 21 |

| 5. 1. 上电复位 .....           | 21 |

| 5. 2. 掉电复位掉 .....          | 21 |

| 5. 3. 看门狗复位 .....          | 21 |

| 5. 3. 1. 控制寄存器列表 .....     | 21 |

| 5. 3. 2. 寄存器详细说明 .....     | 22 |

| 5. 4. 低电检测复位 .....         | 24 |

| 5. 4. 1. 控制寄存器列表 .....     | 24 |

| 5. 4. 2. 寄存器详细说明 .....     | 24 |

| 6. 低功耗管理 .....             | 27 |

| 6. 1. Idle Mode 及唤醒 .....  | 28 |

| 6. 2. Stop Mode 及唤醒 .....  | 28 |

| 6. 3. Sleep Mode 及唤醒 ..... | 28 |

| 6. 4. 低功耗唤醒单元结构图 .....     | 28 |

| 7. 系统控制模块 .....            | 29 |

| 7. 1. 功能概述 .....           | 29 |

| 7. 2. 寄存器列表 .....          | 29 |

| 7. 3. 寄存器详细说明 .....        | 31 |

| 7. 3. 1. SYS_CON0 .....    | 31 |

| 7. 3. 2. SYS_CON1 .....    | 31 |

| 7. 3. 3. SYS_CON2 .....    | 32 |

| 7. 3. 4. SYS_CON3 .....    | 33 |

| 7. 3. 5. SYS_CON4 .....    | 34 |

| 7. 3. 6. SYS_CON5 .....    | 35 |

| 7. 3. 7. CLK_CON0 .....    | 36 |

| 7. 3. 8. CLK_CON1 .....    | 37 |

| 7. 3. 9. CLK_CON2 .....    | 38 |

| 7. 3. 10. CLK_CON3 .....   | 38 |

| 7. 3. 11. CLK_CON4 .....   | 39 |

| 7. 3. 12. CLK_CON5 .....   | 40 |

| 7. 3. 13. CLK_CON6 .....   | 40 |

| 7. 3. 14. AIP_CON0 .....   | 41 |

| 7. 3. 15. AIP_CON1 .....   | 41 |

| 7. 3. 16. AIP_CON2 .....   | 42 |

| 7. 3. 17. AIP_CON3 .....   | 42 |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                           |    |

|---------------------------|----|

| 7. 3. 18. AIP_CON4 .....  | 42 |

| 7. 3. 19. IO_MAP .....    | 42 |

| 7. 3. 20. IO_MAP1 .....   | 43 |

| 7. 3. 21. WKUP_CON0 ..... | 44 |

| 7. 3. 22. WKUP_PND .....  | 45 |

| 7. 3. 23. LP_CON .....    | 46 |

| 7. 3. 24. SYS_PND .....   | 47 |

| 8. 中断系统 .....             | 47 |

| 8. 1. 中断概述 .....          | 47 |

| 8. 2. 结构框图 .....          | 48 |

| 8. 3. 中断向量表 .....         | 49 |

| 8. 4. 寄存器列表 .....         | 49 |

| 8. 5. 寄存器详细说明 .....       | 50 |

| 8. 5. 1. IE0 .....        | 50 |

| 8. 5. 2. IE1 .....        | 51 |

| 8. 5. 3. IP0 .....        | 52 |

| 8. 5. 4. IP1 .....        | 52 |

| 8. 6. 中断优先级及中断嵌套 .....    | 53 |

| 9. I/O 端口 .....           | 54 |

| 9. 1. 结构框图 .....          | 54 |

| 9. 2. 寄存器列表 .....         | 54 |

| 9. 3. 寄存器详细说明 .....       | 56 |

| 9. 3. 1. P0 .....         | 56 |

| 9. 3. 2. P0_PU .....      | 56 |

| 9. 3. 3. P0_PD .....      | 57 |

| 9. 3. 4. P0_MD0 .....     | 58 |

| 9. 3. 5. P0_MD1 .....     | 59 |

| 9. 3. 6. P0_AF0 .....     | 59 |

| 9. 3. 7. P0_AF1 .....     | 60 |

| 9. 3. 8. P0_TRG0 .....    | 61 |

| 9. 3. 9. P0_TRG1 .....    | 62 |

| 9. 3. 10. P0_PND .....    | 63 |

| 9. 3. 11. P0_IMK .....    | 64 |

| 9. 3. 12. P0_AIOEN .....  | 64 |

| 9. 3. 13. P0_DRV .....    | 65 |

| 9. 3. 14. P0_OD .....     | 66 |

| 9. 3. 15. P1 .....        | 67 |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                           |    |

|---------------------------|----|

| 9.3.16. P1_PU .....       | 67 |

| 9.3.17. P1_PD .....       | 68 |

| 9.3.18. P1_MD0 .....      | 69 |

| 9.3.19. P1_MD1 .....      | 70 |

| 9.3.20. P1_AF0 .....      | 70 |

| 9.3.21. P1_AF1 .....      | 71 |

| 9.3.22. P1_TRG0 .....     | 71 |

| 9.3.23. P1_TRG1 .....     | 72 |

| 9.3.24. P1_PND .....      | 73 |

| 9.3.25. P1_IMK .....      | 74 |

| 9.3.26. P1_AIOEN .....    | 74 |

| 9.3.27. P1_DRV .....      | 75 |

| 9.3.28. P1_OD .....       | 76 |

| 10. SPI 模块 .....          | 77 |

| 10.1. 功能概述 .....          | 77 |

| 10.2. 模块框图 .....          | 77 |

| 10.3. 寄存器列表 .....         | 78 |

| 10.4. 寄存器详细说明 .....       | 78 |

| 10.4.1. SPI0_CON .....    | 78 |

| 10.4.2. SPI0_BAUD .....   | 79 |

| 10.4.3. SPI0_DATA .....   | 79 |

| 10.4.4. SPI0_STA .....    | 79 |

| 10.5. 使用流程说明 .....        | 80 |

| 11. UART0/1 模块 .....      | 80 |

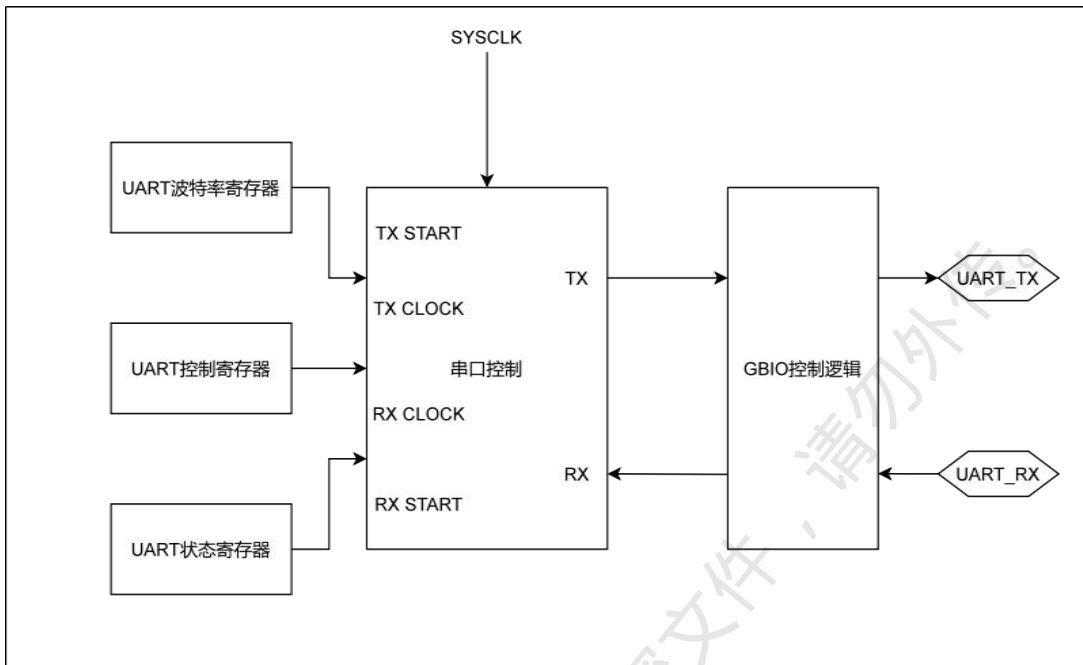

| 11.1. 功能概述 .....          | 80 |

| 11.2. 模块框图 .....          | 81 |

| 11.3. 寄存器列表 .....         | 81 |

| 11.4. 寄存器详细说明 .....       | 82 |

| 11.4.1. UART0_CON .....   | 82 |

| 11.4.2. UART0_STA .....   | 83 |

| 11.4.3. UART0_BAUD0 ..... | 83 |

| 11.4.4. UART0_BAUD1 ..... | 84 |

| 11.4.5. UART0_DATA .....  | 84 |

| 11.4.6. UART1_CON .....   | 84 |

| 11.4.7. UART1_STA .....   | 85 |

| 11.4.8. UART1_BAUD0 ..... | 86 |

| 11.4.9. UART1_BAUD1 ..... | 86 |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                             |     |

|-----------------------------|-----|

| 11. 4. 10. UART1_DATA ..... | 86  |

| 11. 5. 使用流程说明 .....         | 86  |

| 发送数据: .....                 | 86  |

| 接收数据: .....                 | 87  |

| 12. 基本 Timer 0/1 模块 .....   | 87  |

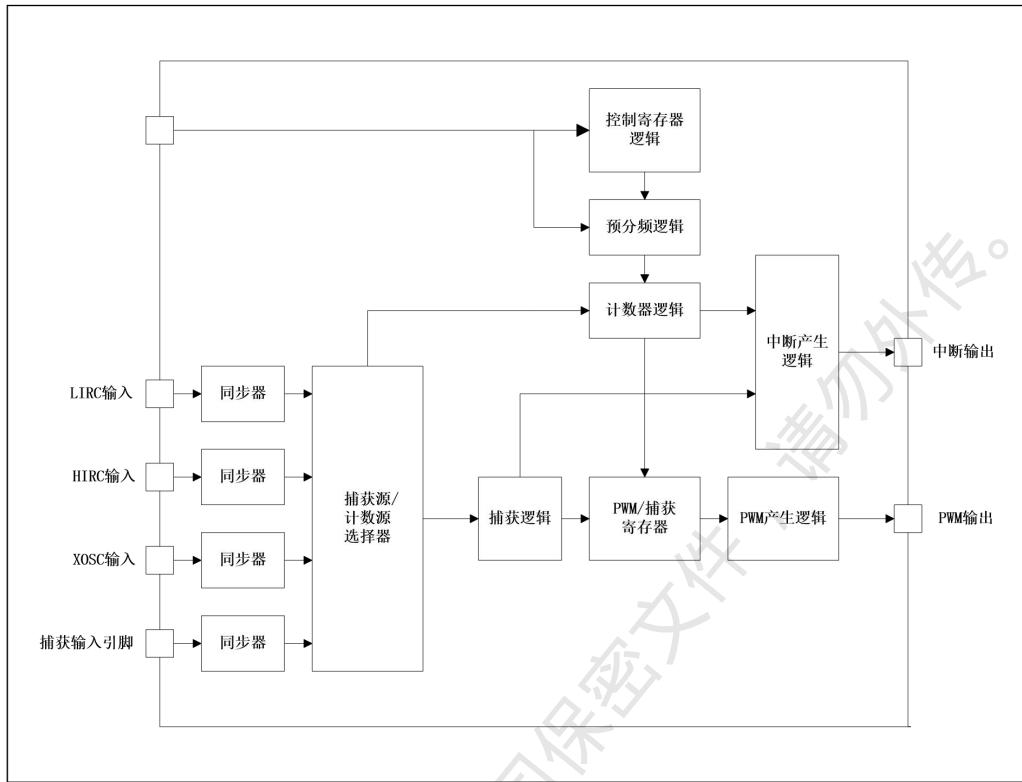

| 12. 1. 功能概述 .....           | 87  |

| 12. 2. 模块框图 .....           | 88  |

| 12. 3. 寄存器列表 .....          | 88  |

| 12. 4. 寄存器详细说明 .....        | 89  |

| 12. 4. 1. TMR0_CONL .....   | 89  |

| 12. 4. 2. TMR0_CONH .....   | 90  |

| 12. 4. 3. TMR0_CNTL .....   | 91  |

| 12. 4. 4. TMR0_PRL .....    | 91  |

| 12. 4. 5. TMR0_PWML .....   | 91  |

| 12. 4. 6. TMR1_CONL .....   | 91  |

| 12. 4. 7. TMR1_CONH .....   | 92  |

| 12. 4. 8. TMR1_CNTL .....   | 93  |

| 12. 4. 9. TMR1_PRL .....    | 93  |

| 12. 4. 10. TMR1_PWML .....  | 93  |

| 12. 5. 使用流程说明 .....         | 94  |

| 12. 5. 1. 计数器/定时器工作模式 ..... | 94  |

| 12. 5. 2. 捕获工作模式 .....      | 94  |

| 12. 5. 3. PWM 工作模式 .....    | 95  |

| 13. 基本 Timer2 模块 .....      | 95  |

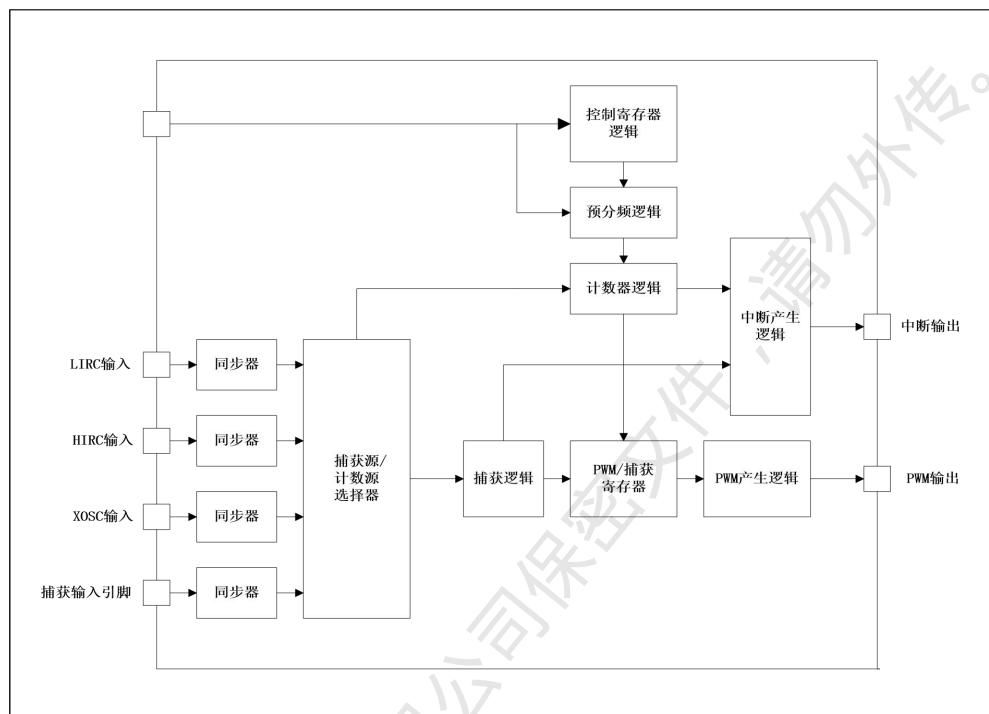

| 13. 1. 功能概述 .....           | 95  |

| 13. 2. 模块框图 .....           | 96  |

| 13. 3. 寄存器列表 .....          | 96  |

| 13. 4. 寄存器详细说明 .....        | 97  |

| 13. 4. 1. TMR2_CONL .....   | 97  |

| 13. 4. 2. TMR2_CONH .....   | 98  |

| 13. 4. 3. TMR2_CNTL .....   | 99  |

| 13. 4. 4. TMR2_CNTH .....   | 99  |

| 13. 4. 5. TMR2_PRL .....    | 99  |

| 13. 4. 6. TMR2_PRH .....    | 99  |

| 13. 4. 7. TMR2_PWML .....   | 99  |

| 13. 4. 8. TMR2_PWMH .....   | 100 |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                             |     |

|-----------------------------|-----|

| 13.5. 使用流程说明 .....          | 100 |

| 13.5.1. 计数器/定时器工作模式 .....   | 100 |

| 13.5.2. 捕获工作模式 .....        | 101 |

| 13.5.3. PWM 工作模式 .....      | 101 |

| 14. 高级 Timer 1/2 模块 .....   | 102 |

| 14.1. 功能概述 .....            | 102 |

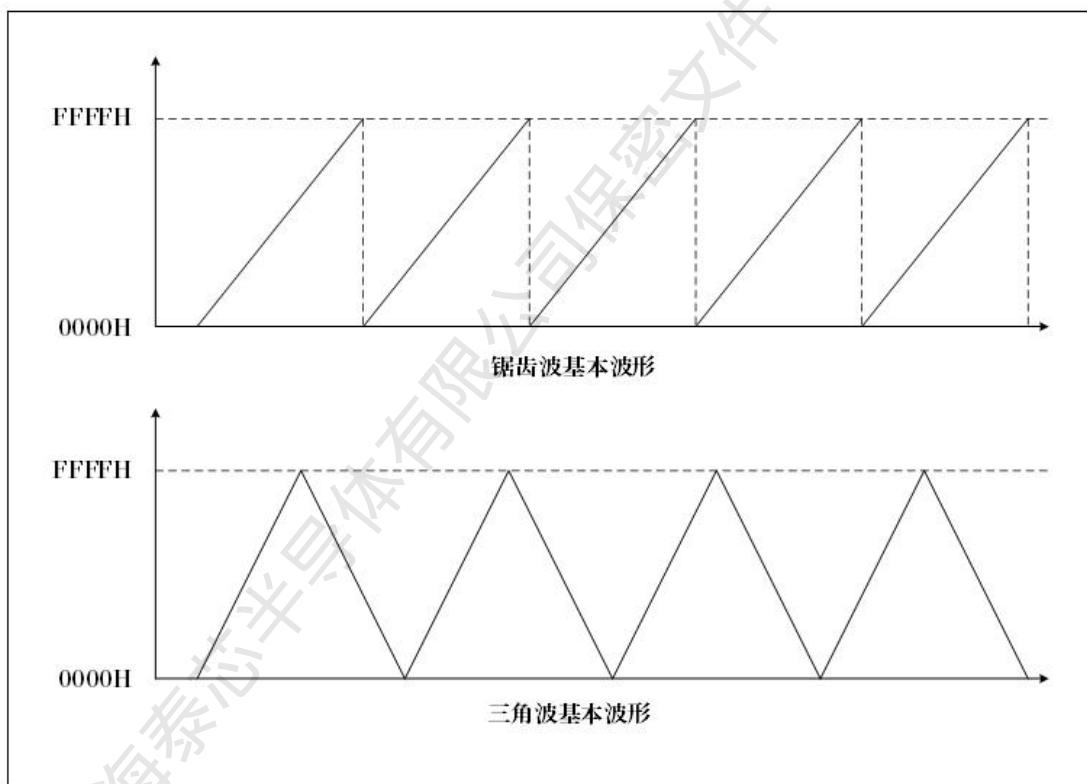

| 14.1.1. 基本动作 .....          | 103 |

| 14.1.2. 时钟源选择 .....         | 105 |

| 14.1.3. 计数方向 .....          | 106 |

| 14.1.4. 数字滤波 .....          | 107 |

| 14.1.5. 软件同步 .....          | 107 |

| 14.1.6. 缓存功能 .....          | 109 |

| 14.1.7. 通用 PWM 输出 .....     | 110 |

| 14.1.8. 周期间隔响应 .....        | 112 |

| 14.1.9. 保护机制 .....          | 113 |

| 14.1.10. 中断说明 .....         | 114 |

| 14.1.11. 刹车保护 .....         | 114 |

| 14.1.12. 内部互连 .....         | 114 |

| 14.1.13. 红外功能 .....         | 114 |

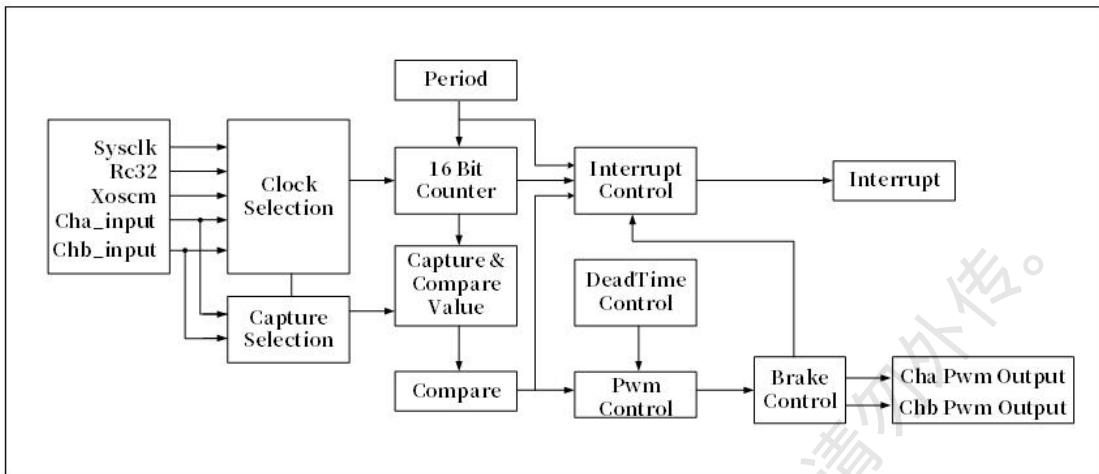

| 14.2. 模块框图 .....            | 115 |

| 14.3. 寄存器列表 .....           | 115 |

| 14.4. 寄存器详细说明 .....         | 117 |

| 14.4.1. STMR1_CR .....      | 117 |

| 14.4.2. STMR1_FCONR .....   | 118 |

| 14.4.3. STMR1_CNTL .....    | 118 |

| 14.4.4. STMR1_CNTH .....    | 119 |

| 14.4.5. STMR1_PRL .....     | 119 |

| 14.4.6. STMR1_PRH .....     | 119 |

| 14.4.7. STMR1_CMPAL .....   | 119 |

| 14.4.8. STMR1_CMPAH .....   | 119 |

| 14.4.9. STMR1_CMPBL .....   | 120 |

| 14.4.10. STMR1_CMBPH .....  | 120 |

| 14.4.11. STMR1_VPERR .....  | 120 |

| 14.4.12. STMR1_DTUA .....   | 121 |

| 14.4.13. STMR1_BRAKE .....  | 121 |

| 14.4.14. STMR1_DTR .....    | 122 |

| 14.4.15. STMR1_PCONRA ..... | 123 |

| 14.4.16. STMR1_PCONRB ..... | 124 |

| 14.4.17. STMR1_IE .....     | 125 |

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                               |            |

|-------------------------------|------------|

| 14. 4. 18. STMR1_SR .....     | 126        |

| 14. 4. 19. STMR2_CR .....     | 127        |

| 14. 4. 20. STMR2_FCONR .....  | 128        |

| 14. 4. 21. STMR2_PRL .....    | 128        |

| 14. 4. 22. STMR2_PRH .....    | 129        |

| 14. 4. 23. STMR2_CMPAL .....  | 129        |

| 14. 4. 24. STMR2_CMPAH .....  | 129        |

| 14. 4. 25. STMR2_CMPBL .....  | 129        |

| 14. 4. 26. STMR2_CMPBH .....  | 130        |

| 14. 4. 27. STMR2_VPERR .....  | 130        |

| 14. 4. 28. STMR2_DTUA .....   | 131        |

| 14. 4. 29. STMR2_BRAKE .....  | 131        |

| 14. 4. 30. STMR2_DTR .....    | 132        |

| 14. 4. 31. STMR2_PCONRA ..... | 133        |

| 14. 4. 32. STMR2_PCONRB ..... | 134        |

| 14. 4. 33. STMR2_IE .....     | 135        |

| 14. 4. 34. STMR2_SR .....     | 136        |

| 14. 4. 35. STMR_ALLCON .....  | 137        |

| 14. 5. 使用流程说明 .....           | 137        |

| <b>15. CRC16 模块 .....</b>     | <b>138</b> |

| 15. 1. 功能概述 .....             | 138        |

| 15. 2. 基本功能 .....             | 138        |

| 15. 3. 模块框图 .....             | 139        |

| 15. 4. 寄存器列表 .....            | 139        |

| 15. 5. 寄存器详细说明 .....          | 139        |

| 15. 5. 1. CRC_REG .....       | 139        |

| 15. 5. 2. CRC_FIFO .....      | 140        |

| 15. 6. 使用流程说明 .....           | 140        |

| <b>16. FLASH 控制器模块 .....</b>  | <b>140</b> |

| 16. 1. 功能概述 .....             | 140        |

| 16. 2. 模块框图 .....             | 141        |

| 16. 3. 寄存器列表 .....            | 141        |

| 16. 4. 寄存器详细说明 .....          | 142        |

| 16. 4. 1. FLASH_CON .....     | 142        |

| 16. 4. 2. FLASH_STA .....     | 142        |

| 16. 4. 3. FLASH_DATA .....    | 143        |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                              |     |

|------------------------------|-----|

| 16. 4. 4. FLASH_TIM0 .....   | 143 |

| 16. 4. 5. FLASH_TIM1 .....   | 144 |

| 16. 4. 6. FLASH_CRCLEN ..... | 145 |

| 16. 4. 7. FLASH_PSWD .....   | 145 |

| 16. 4. 8. FLASH_ADDR .....   | 146 |

| 16. 4. 9. FLASH_TRIM .....   | 146 |

| 16. 5. 使用流程说明 .....          | 146 |

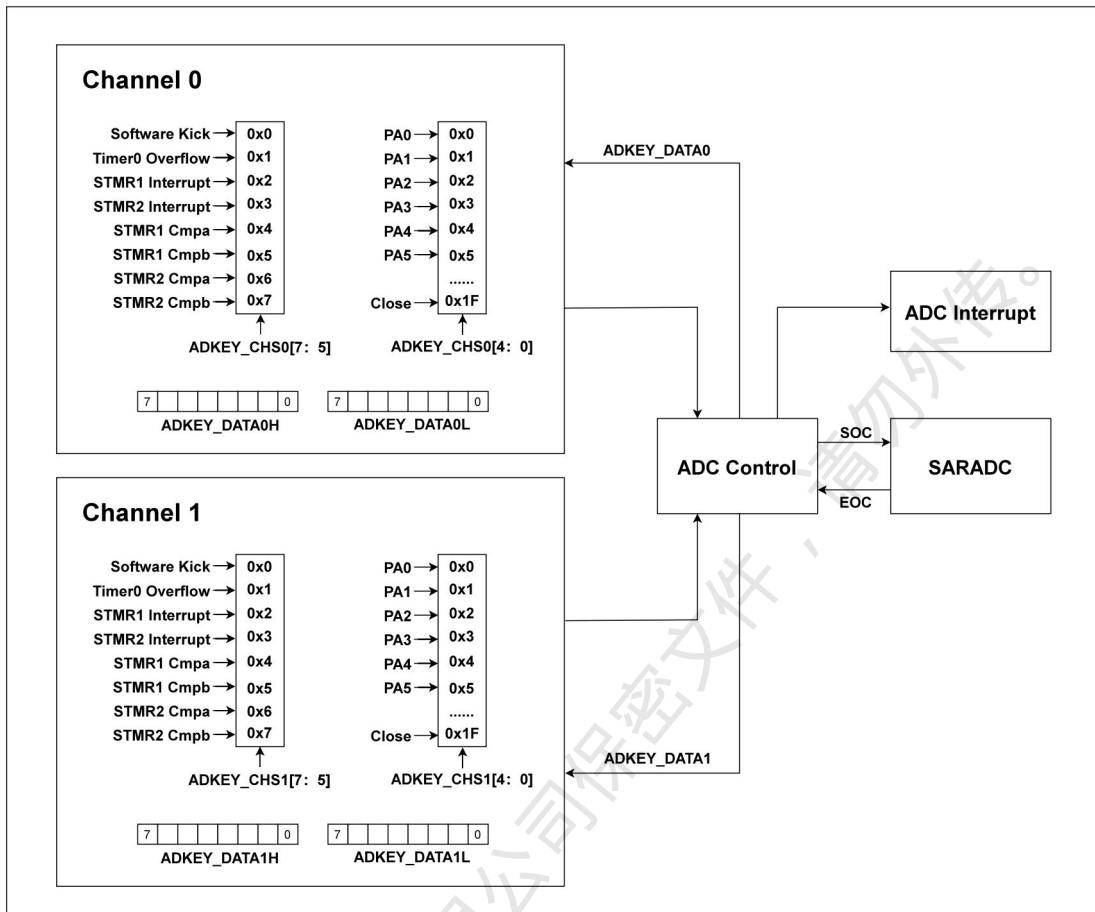

| 17. 模数转换器(ADC) .....         | 147 |

| 17. 1. 功能概述 .....            | 147 |

| 17. 2. 基本功能 .....            | 148 |

| 17. 2. 1. 单通道触发模式 .....      | 148 |

| 17. 2. 2. 双通道触发模式 .....      | 148 |

| 17. 2. 3. 单通道触发延迟模式 .....    | 148 |

| 17. 2. 4. 模拟校准/数字校准 .....    | 149 |

| 17. 3. 模块框图 .....            | 150 |

| 17. 4. 寄存器列表 .....           | 150 |

| 17. 5. 寄存器详细说明 .....         | 151 |

| 17. 5. 1. ADC_CFG0 .....     | 151 |

| 17. 5. 2. ADC_CFG1 .....     | 152 |

| 17. 5. 3. ADC_CFG2 .....     | 153 |

| 17. 5. 4. ADC_CFG3 .....     | 153 |

| 17. 5. 5. ADC_STA .....      | 154 |

| 17. 5. 6. ADC_DATAHO .....   | 154 |

| 17. 5. 7. ADC_DATALO .....   | 155 |

| 17. 5. 8. ADC_DATAH1 .....   | 155 |

| 17. 5. 9. ADC_DATAL1 .....   | 155 |

| 17. 5. 10. ADC_CHS0 .....    | 155 |

| 17. 5. 11. ADC_CHS1 .....    | 156 |

| 17. 6. 使用流程说明 .....          | 158 |

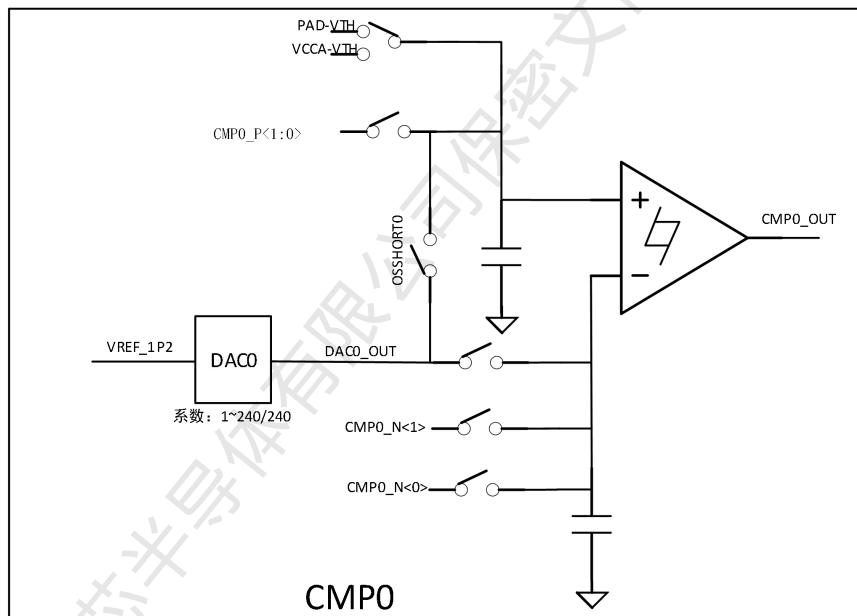

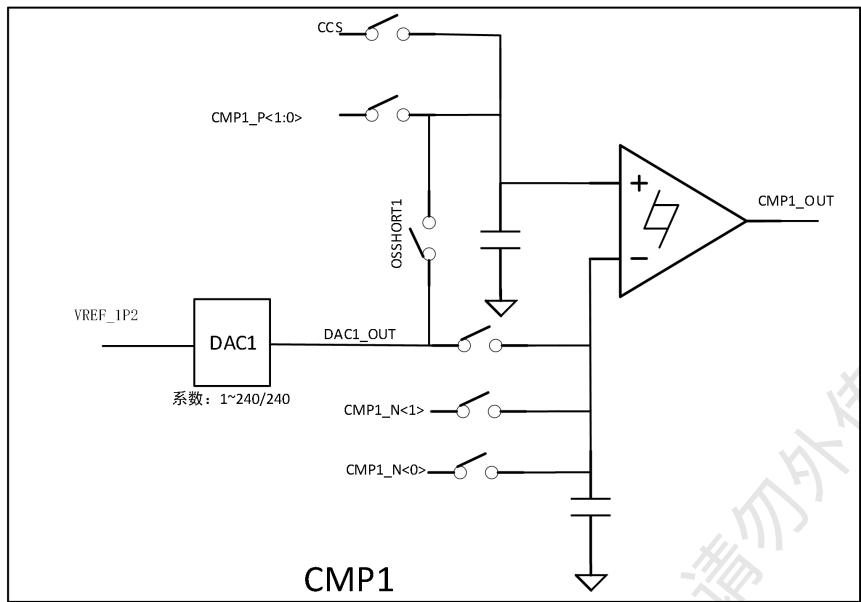

| 18. 模拟比较器(CMP0/1) .....      | 158 |

| 18. 1. 功能概述 .....            | 158 |

| 18. 2. 模块框图 .....            | 159 |

| 18. 3. 引脚对应表 .....           | 160 |

| 18. 4. 寄存器列表 .....           | 161 |

| 18. 5. 寄存器详细说明 .....         | 162 |

| 18. 5. 1. CMP0_CON0 .....    | 162 |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                               |            |

|-------------------------------|------------|

| 18.5.2. CMP0_CON1 .....       | 162        |

| 18.5.3. CMP0_CON2 .....       | 163        |

| 18.5.4. CMP0_CON3 .....       | 164        |

| 18.5.5. CMP0_CON4 .....       | 165        |

| 18.5.6. CMP0_DAC0 .....       | 165        |

| 18.5.7. CMP0_DAC1 .....       | 166        |

| 18.5.8. CMP1_CON0 .....       | 166        |

| 18.5.9. CMP1_CON1 .....       | 167        |

| 18.5.10. CMP1_CON2 .....      | 167        |

| 18.5.11. CMP1_CON3 .....      | 168        |

| 18.5.12. CMP1_CON4 .....      | 169        |

| 18.5.13. CMP1_DAC0 .....      | 169        |

| 18.5.14. CMP1_DAC1 .....      | 170        |

| 18.5.15. CMP_CON .....        | 170        |

| 18.5.16. CMP_STA .....        | 171        |

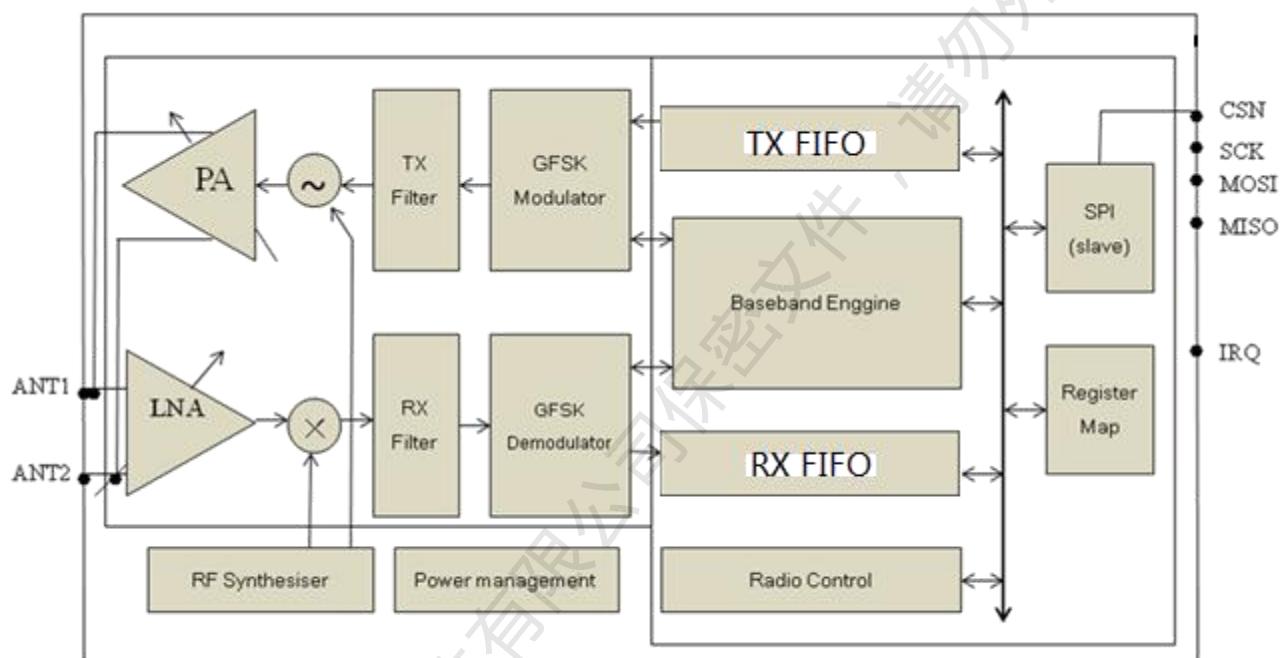

| <b>19.2.4G RF 收发器模块 .....</b> | <b>172</b> |

| 19.1. 功能描述 .....              | 172        |

| ● 无线部分特性 .....                | 172        |

| ● 射频综合器 .....                 | 172        |

| ● 发射器 .....                   | 172        |

| ● 接收器 .....                   | 172        |

| 19.2. 模块框图 .....              | 173        |

| 19.3. 寄存器列表 .....             | 173        |

| 19.4. 寄存器详细说明 .....           | 175        |

| 19.4.1. CONFIG .....          | 175        |

| 19.4.2. EN_AA .....           | 176        |

| 19.4.3. EN_RXADDR .....       | 177        |

| 19.4.4. PMU_CTL .....         | 177        |

| 19.4.5. SETUP_RETR .....      | 178        |

| 19.4.6. RF_CH .....           | 179        |

| 19.4.7. RF_SETUP .....        | 179        |

| 19.4.8. STATUS .....          | 180        |

| 19.4.9. RX_ADDR_P0 .....      | 181        |

| 19.4.10. RX_ADDR_P1 .....     | 181        |

| 19.4.11. RX_ADDR_P2 .....     | 181        |

| 19.4.12. TX_ADDR .....        | 181        |

| 19.4.13. RX_PW_P0 .....       | 182        |

| 19.4.14. RX_PW_P1 .....       | 182        |

| 19.4.15. RX_PW_P2 .....       | 183        |

| 19.4.16. FIFO_STATUS .....    | 184        |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

|      |            |               |      |                     |

|------|------------|---------------|------|---------------------|

| 保密等级 | A          | TX8W7010 用户手册 | 文件编号 | TX-WI-TX8W7010-RD02 |

| 发行日期 | 2022-08-10 |               | 文件版本 | V1.5                |

|                              |     |

|------------------------------|-----|

| 19. 4. 17. CONFIG_EXT .....  | 184 |

| 19. 4. 18. DYNPD .....       | 185 |

| 19. 4. 19. FEATURE .....     | 185 |

| 19. 4. 20. SETUP_VALUE ..... | 186 |

| 19. 4. 21. PRE_GURD .....    | 186 |

| 19. 4. 22. LINE .....        | 187 |

| 19. 4. 23. PLL_CTL0 .....    | 187 |

| 19. 4. 24. PLL_CTL1 .....    | 190 |

| 19. 4. 25. CAL_CTL .....     | 191 |

| 19. 4. 26. STATUS .....      | 192 |

| 19. 4. 27. STATE .....       | 193 |

| 19. 4. 28. CHAN .....        | 193 |

| 19. 4. 29. FDEV .....        | 194 |

| 19. 4. 30. DAC_RANGE .....   | 194 |

| 19. 4. 31. CTUNING .....     | 194 |

| 19. 4. 32. FTUNING .....     | 195 |

| 19. 4. 33. RX_CTRL .....     | 195 |

| 19. 4. 34. FAGC_CTRL_1 ..... | 196 |

| 19. 4. 35. DOC_DACI .....    | 196 |

| 19. 4. 36. DOC_DACQ .....    | 197 |

| 19. 4. 37. AGC_CTRL .....    | 197 |

| 19. 4. 38. AGC_GAIN .....    | 198 |

| 19. 4. 39. RF_IVGEN .....    | 198 |

| 19. 4. 40. TEST_PKDET .....  | 200 |

| 19. 5. 应用使用说明 .....          | 200 |

| 19. 5. 1. 普通 2.4G 模式 .....   | 200 |

珠海泰芯半导体有限公司

Zhuhai Taixin Semiconductor Co., Ltd

珠海市高新区港湾一号科创园港 11 栋 3 楼

# 1. 产品概述

## 1.1. 说明

TX8W7010 是一款支持 2.4G 无线通信功能，高性能低功耗的 8051 内核的无线 MCU，工作主频最高为 32MHz，内置 4K+256 字节闪存存储器（支持类 EEPROM），512 字节 SRAM。

TX8W7010 是一款嵌入基带通信协议的单片 2.4GHz 收发芯片，工作在 2.4GHz~2.483GHz 世界通用的 ISM 频段，适用于超低功耗无线应用领域。该芯片集成了射频收发器、频率合成器、多通信模式控制器、调制器、解调器等功能模块。可以对输出功率、频道选择以及协议的设置等用途进行灵活配置。采用 GFSK, FSK 调制，支持 2Mbps, 1Mbps 的数据速率，最大发射功率可以达到 8dBm，接收灵敏度在 1Mbps 速率下可以达到 -90dBm。

模拟资源： 1 个 12 位 200Ksps 的 ADC、2 个多功能比较器

定时器、PWM 资源（两者是互斥功能，同一个 Timer 不能同时使用）：

- 2 个 16 位高级定时器，能支持 2 对互补输出或 4 个独立 PWM 输出（周期相同，占空比独立配置）

- 1 个 16 位通用定时器（都支持 Capture、Count、PWM 功能）

- 2 个 8 位通用定时器（可合成 1 个 16 位通用定时器，都支持 Capture、Count、PWM 功能）

标准的通信接口：1 个 SPI 接口和 2 个 UART 接口。

支持宽范围电压供电，工作电压为 2.4V ~ 3.6V，工作温度范围 -40°C ~ 85°C。多种省电工作模式保证低功耗应用的要求，最低功耗模式 5uA。

TX8W7010 提供 SOP16 封装形式，应用场合：

- 无线鼠标和键盘

- 玩具和无线音频

- 无线游戏手柄

- 有源无线标签

- 智能家居及安防系统

- 电视和机顶盒遥控

- 无线工控

- 无线航模

## 1.2. 特性

- **内核**

- 超高速 8051 内核 (1T)

- 指令全兼容传统 8051

- 工作最大主频: 32MHz

- 14 个中断源, 支持硬件两级优先级

- 支持在线下载

- **工作电压**

- 2.4V~3.6V 电压范围供电

- **存储器**

- 4K+256 字节 Flash, 用于存储用户代码, 并且支持类 EEPROM (擦写次数典型值 10 万次)

- 512 字节 RAM

- **时钟**

- 内部 1~32MHz 高精度 HIRC, 支持校准 (误差±1%)

- 内部 64KHz 低速 LIRC, 支持校准 (误差±1%)

- 外部 32.768 KHz 低速晶振, 需要外部加电容

- **复位**

- 上电复位

- 欠压复位

- 复位脚复位

- 看门狗溢出复位

- **GPIO**

- 最多可达 9 个 GPIO

- 所有端口均可输入输出 3.3V 信号

- 均支持上升沿/下降沿/双边沿中断

- 均支持唤醒功能

- 有全驱动和小驱动两个档位。

- 支持 OD 输出低模式。

- 支持独立控制的上下拉电阻，阻值 30KΩ

- **LVD 低压检测复位**

- 提供 4 级低压检测电压 (1.85/2.03V、2.15/2.34V、2.43/2.63V、3.34/3.63V)

- **数字外设**

- 1 个 SPI 高速串行接口，支持主从模式

- 2 个 UART 接口，最大支持 4Mbps

- **定时器资源**

- 2 个 16 位高级定时器，能支持 2 对互补输出或 4 个独立 PWM 输出（周期相同，占空比独立配置），支持死区插入和事件刹车功能，支持单脉冲模式

- 1 个 16 位通用定时器，都支持 Capture、Count、PWM 功能

- 2 个 8 位通用定时器（可合成 1 个 16 位通用定时器，都支持 Capture、Count、PWM 功能），可以支持红外发送和接收功能（需要两个 Timer）

- 1 个看门狗定时器

- **高安全性**

- 支持 16 bit CRC 效验，保证数据准确性

- **低功耗**

- 支持 Idle、Stop、Sleep 低功耗模式

- 静态功耗 5uA @25°C

- 低功耗唤醒时间小于 100us

- **2 个模拟比较器(ACMP)**

- 2 个低失调比较器，校正 step 1mV

- 比较器支持负端输入精准 BG 的 120 个分压档位

- 两个比较器都支持轨到轨输入模式，正负端各支持 2 个 GPIO 可选

- 支持短路保护

- **无线部分特性**

- 通信频段：2.400GHz ~ 2.483GHz

- 支持 BLE 广播包

- 支持长包模式（最大 255Byte）

- 数据速率：2Mbps, 1Mbps

- 调制方式：GFSK, FSK

- 126 个射频信道

- **射频综合器**

- 完全集成频率合成器

- 不需要外部环路滤波器 (LF) 和压控振荡器 (VCO)

- 可接受低成本的晶体：±60ppm 16MHz 晶体

- **发射器**

- 可编程的发射功率：-34 ~ +8 dBm

- 发射功率为 0dBm 时，工作电流为 17mA

- **接收器**

- 快速 AGC 功能

- 集成通道滤波器

- 空口速率为 2Mbps 时，工作电流为 18mA

- 空口速率为 2Mbps 时，接收灵敏度为 -87dBm

- 空口速率为 1Mbps 时，接收灵敏度为 -90dBm

- **高可靠性**

- ESD HBM 6KV

- Latch-up ±200mA @25°C

- **96 位的芯片唯一 ID (UID)**

- **封装**

- SOP16

- **工作温度范围**

➤ -40°C ~ 85°C

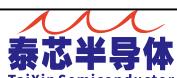

### 1.3. 引脚分配

图 1-1 TX8W7010S016 引脚图

### 1.4. 封装信息

TX8W7010 系列的型号如下表格：

| 型号           | 封装    | 包装 |

|--------------|-------|----|

| TX8W7010S016 | SOP16 | 管装 |

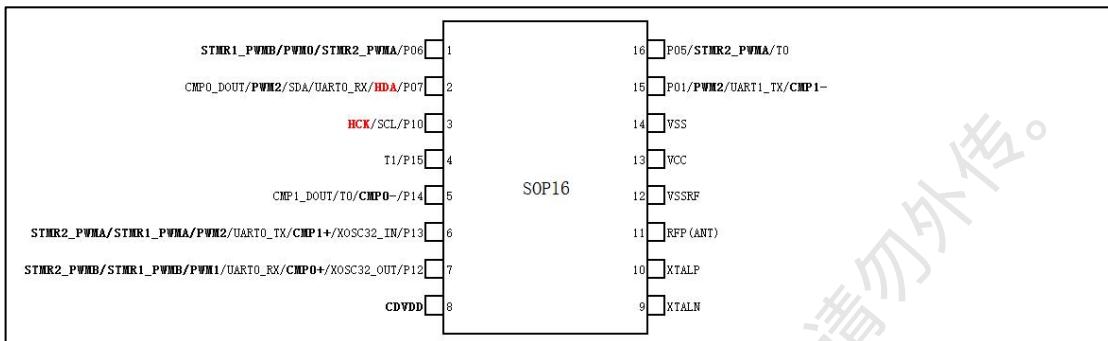

### 1.5. 封装尺寸图

图 1-2 SOP16 封装 POD 图

## 1.6. 引脚说明

| 引脚名字  | I/O | 功能描述                                          | 复位状态      | 复用功能                                                                                              |

|-------|-----|-----------------------------------------------|-----------|---------------------------------------------------------------------------------------------------|

| XTALP | A   | 16MHz 晶振输入                                    | —         | 无                                                                                                 |

| XTALN | A   | 16MHz 晶振输出                                    | —         | 无                                                                                                 |

| RFP   | A   | RF 天线                                         | —         | 无                                                                                                 |

| CDVDD | A   | RF VDD 输出, 外接一个退耦电容                           | —         | 无                                                                                                 |

| VCC   | A   | 供电电源 2.4V ~ 3.6V                              | —         | 无                                                                                                 |

| VSS   | A   | 地                                             | —         | 无                                                                                                 |

| VSSRF | A   | RF 地                                          | —         | 无                                                                                                 |

| P01   | I/O | PO 口每个口都可以设置为输入或者输出模式输入模块可以使能内部上拉输出模块可以设置开漏输出 | 引脚默认为高阻输入 | P01<br>PWM2【Timer2 的 PWM 输出】<br>UART1_TX【UART1 TX 发送引脚】<br>HDA【烧写/调试数据引脚】<br>CMP1-【比较器 1 的负端输入引脚】 |

|     |     |                                               |                          |                                                                                                                                                                                           |

|-----|-----|-----------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P05 |     |                                               |                          | P05<br>STMR2_PWM_A【高级 Timer2 的 CHA PWM 输出】<br>TO【通用 Timer0 的捕获输入引脚】                                                                                                                       |

| P06 |     |                                               |                          | P06<br>STMR1_PWM_B【高级 Timer1 的 CHB PWM 输出】<br>PWMO【Timer0 的 PWM 输出】<br>STMR2_PWM_A【高级 Timer2 的 CHA PWM 输出】                                                                                |

| P07 |     |                                               |                          | P07<br>SDA【IIC 的数据引脚】<br>CMPO_DOUT【比较器0的数字输出引脚】<br>PWM2【Timer2的PWM输出】<br>UARTO_RX【UARTO_RX接收】<br>HDA【烧写/调试数据引脚】                                                                           |

| P10 | I/O | P1 口每个口都可以设置为输入或者输出模式输入模块可以使能内部上拉输出模块可以设置开漏输出 | P10 默认认为上拉打开，其他引脚默认为高阻输入 | P10<br>HCK【烧写/调试时钟引脚】<br>SCL【IIC 的时钟引脚】                                                                                                                                                   |

| P12 |     |                                               |                          | P12<br>STMR2_PWM_B【高级 Timer2 的 CHB PWM 输出】<br>STMR1_PWM_B【高级 Timer1 的 CHB PWM 输出】<br>PWM1【Timer1的PWM输出】<br>UARTO_RX【UARTO_RX接收】<br>CMPO+【比较器0的正端输入引脚】<br>XOSC32_O【外部 32.768KHz 晶振输出引脚】    |

| P13 |     |                                               |                          | P13<br>STMR2_PWM_A【高级 Timer2 的 CHA PWM 输出】<br>STMR1_PWM_A【高级 Timer1 的 CHA PWM 输出】<br>PWM2【Timer2的PWM输出】<br>UARTO_TX【UARTO_TX发送引脚】<br>CMP1+【比较器1的正端输入引脚】<br>XOSC32_IN【外部 32.768KHz 晶振输入引脚】 |

| P14 |     |                                               |                          | P14<br>CMP1_DOUT【比较器1的数字输出引脚】<br>TO【通用 Timer0 的捕获输入引脚】<br>CMPO-【比较器0的负端输入引脚】                                                                                                              |

|     |  |  |  |                                               |

|-----|--|--|--|-----------------------------------------------|

| P15 |  |  |  | P15                                           |

|     |  |  |  | CMPO_DOUT【比较器0的数字输出引脚】<br>T1【通用Timer1的捕获输入引脚】 |

## 2. 中央处理器

TX8W7010 全兼容传统的 8051 微控制器，所有指令的助记符和二进制码都和 8051 兼容。

TX8W7010 的处理器采用了一些体系结构上的优化，扩展了 SP、DPTR 等常用的寄存器，相比传统的 8051 在性能上面有了很大的提升。

TX8W7010 内部的 ALU 配合内部的 ACC (0xE0)、B (0xF0)、PSW (0xD0) 寄存器可以实现各种 8 位运算操作。

ALU 可以进行典型操作如下：

- 基本算术运算：加法、减法、乘法、除法

- 其他算术运算：自加、自减、BCD 调整、比较

- 逻辑运算：与、或、异或、取反、移位

- 布尔比特运算：置位、清零、取反、按位判断跳转、进位操作

### 2.1. 累加器 (ACC)

ALU 是 8Bit 宽的算术逻辑单元，MCU 所有的数学、逻辑运算均通过它来完成。它可以对数据进行加、减、移位及逻辑运算；ALU 也控制状态位（PSW 状态寄存器中），用来表示运算结果的状态。

ACC 寄存器是一个 8Bit 的寄存器，ALU 的运算结果可以存放在此。

Addr = 0xE0 (SFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:0    | ACC  | 累加器寄存器      | RW  | 0x0   |

## 2.2. 寄存器 (B)

B 寄存器在使用乘法和除法指令时使用, 乘法结果高 8bit, 除法结果低 8bit。如不使用乘除法指令, 也可作为通用寄存器使用。

Addr = 0xF0 (SFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:0    | B    | B 寄存器       | RW  | 0x0   |

## 2.3. 堆栈指针寄存器 (SP)

SP 寄存器指向堆栈的低 8bit 地址, 复位后默认值为 0x07, 该 SP 的值可以修改。影响 SP 的操作有: 指令 PUSH、LCALL、ACALL、POP、RET、RETI 以及进入中断。

Addr = 0x81 (SFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:0    | SP   | 堆栈指针寄存器     | RW  | 0x7   |

## 2.4. 堆栈指针寄存器 (SPH)

SPH 寄存器指向堆栈高 8bit 地址, 有效位 1bit, 复位后默认值位 0x0, 与 SP 组合使用, 意味着堆栈的区域从 RAM 地址的 0x07 开始。该值可以修改, 如果将堆栈区域设置为 0x0B 开始, 则在复位后将 SPH 和 SP 的值分别设置为 0x0 和 0xA。

影响 SPH 的操作有: 指令 PUSH、LCALL、ACALL、POP、RET、RETI 以及进入中断。

Addr = 0x9B (SFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:1    | -    | -           | -   | -     |

| 0      | SPH  | 堆栈指针寄存器高位   | RW  | 0x0   |

## 2.5. 数据指针寄存器 (DPTR0/DPTR1)

数据指针主要用在 MOVX, MOVC 指令中，其作用是定位 RAM 与 ROM 的地址。芯片内部有两个数据指针寄存器 DPTR0 与 DPTR1，通过 DPSEL 寄存器选择。

每组指针包括两个 8 位寄存器：DPTR0={DPH0, DPL0}、DPTR1={DPH1, DPL1}。

Addr = 0x82 (SFR)

| Bit(s) | Name | Description      | R/W | Reset |

|--------|------|------------------|-----|-------|

| 7:0    | DPL0 | DPTR0 数据指针寄存器低八位 | RW  | 0x0   |

Addr = 0x83 (SFR)

| Bit(s) | Name | Description      | R/W | Reset |

|--------|------|------------------|-----|-------|

| 7:0    | DPH0 | DPTR0 数据指针寄存器高八位 | RW  | 0x0   |

Addr = 0x84 (SFR)

| Bit(s) | Name | Description      | R/W | Reset |

|--------|------|------------------|-----|-------|

| 7:0    | DPL1 | DPTR1 数据指针寄存器低八位 | RW  | 0x0   |

Addr = 0x85 (SFR)

| Bit(s) | Name | Description      | R/W | Reset |

|--------|------|------------------|-----|-------|

| 7:0    | DPL1 | DPTR1 数据指针寄存器高八位 | RW  | 0x0   |

## 2.6. 数据指针控制寄存器 (DPCFG)

Addr = 0x86 (SFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

|        |      |             |     |       |

|     |       |                                                                                                                                                                   |    |     |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 7:6 | IA    | <p><b>中断起始地址和增加方式选择位</b></p> <p>IA[0]</p> <p>0x0: 中断地址= (中断向量*8) +3<br/>0x1: 中断地址= (中断向量+1) *3</p> <p>IA[1]</p> <p>0x0: 中断起始地址为 0x300<br/>0x1: 中断起始地址为 0x8000</p> | RW | 0x2 |

| 5   | DPID0 | <p><b>DPTR0 加 1/减 1</b></p> <p>0x0: DPTR0 加 1<br/>0x1: DPTR0 减 1</p>                                                                                              | RW | 0x0 |

| 4   | DPID1 | <p><b>DPTR1 加 1/减 1</b></p> <p>0x0: DPTR1 加 1<br/>0x1: DPTR1 减 1</p>                                                                                              | RW | 0x0 |

| 3   | DPAID | <p><b>DPTR0/DPTR1 自加自减使能位</b></p> <p>0x0: 关闭<br/>0x1: 打开</p>                                                                                                      | RW | 0x0 |

| 2   | DPTSL | <p><b>DPSEL 自动翻转使能位</b></p> <p>0x0: 关闭<br/>0x1: 打开</p>                                                                                                            | RW | 0x0 |

| 1   | -     | -                                                                                                                                                                 | -  | -   |

| 0   | DPSEL | <p><b>选择 DPTR0 /DPTR1 位</b></p> <p>0x0: DPTR0 有效<br/>0x1: DPTR1 有效</p>                                                                                            | RW | 0x0 |

## 2.7. 程序状态寄存器 (PSW)

Addr = 0xD0 (SFR)

| Bit(s) | Name     | Description                                                         | R/W | Reset |

|--------|----------|---------------------------------------------------------------------|-----|-------|

| 7      | CY       | 进位标志位<br>0x0: 无进位<br>0x1: 有进位                                       | RW  | 0x0   |

| 6      | AC       | 辅助进位标志位<br>0x0: 无进位<br>0x1: 有进位                                     | RW  | 0x0   |

| 5      | F0       | 通用标志位 0                                                             | RW  | 0x0   |

| 4:3    | RS1, RS0 | 寄存器组选择位<br>0x0: 寄存器组 0<br>0x1: 寄存器组 1<br>0x2: 寄存器组 2<br>0x3: 寄存器组 3 | RW  | 0x0   |

| 2      | OV       | 溢出标志位<br>0x0: 算术或逻辑运算无溢出<br>0x1: 算术或逻辑运算有溢出                         | RW  | 0x0   |

| 1      | F1       | 通用标志位 1                                                             | RW  | 0x0   |

| 0      | P        | 奇偶校验标志位<br>0x0: ACC 中 1 为偶数<br>0x1: ACC 中 1 为奇数                     | RW  | 0x0   |

## 2.8. 程序计数器 (PC)

程序计数器 (PC) 控制程序内存 FLASH 中的指令执行顺序，它可以寻址整个 FLASH 的范围，取得指令码后，程序计数器 (PC) 会自动加一，指向下一个指令码的地址。但如果执行跳转、条件跳转、向 PCL 赋值、子程序调用、初始化复位、中断、中断返回、子程序返

回等操作时，PC 会加载与指令相关的地址而不是下一条指令的地址。

当遇到条件跳转指令且符合跳转条件时，当前指令执行过程中读取的下一条指令将会被丢弃，且会插入一个空指令操作周期，随后才能取得正确的指令。反之，就会顺序执行下一条指令。

### 3. 存储器

TX8W7010 有内部有 3 种存储器：IDATA、XDATA、程序存储器。

程序存储只能读不能写，程序存储器大小为 4K 字节。XDATA 大小为 1K 字节（其中 XSFR 为 512 字节），IDATA 大小为 256 字节。

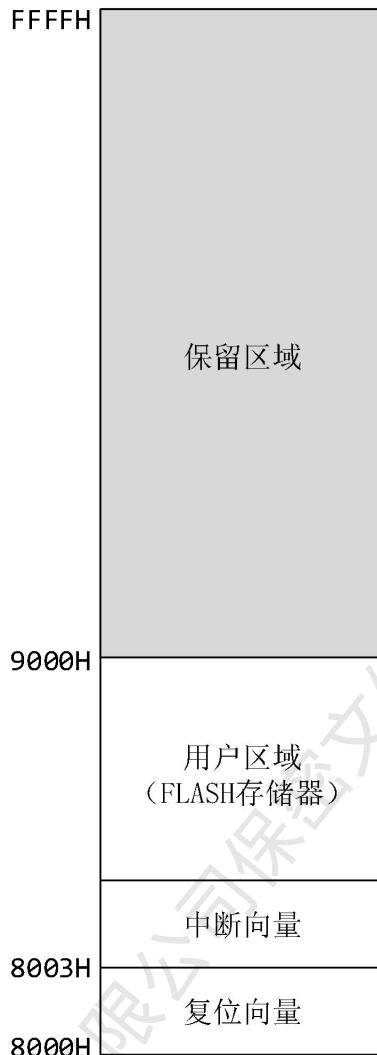

#### 3.1. 程序存储器

TX8W7010 的程序指针为 16 位，最大寻址空间可达 64K 字节，实际只实现了 4K 字节的程序存储空间。

图 3-1 程序存储空间

复位后，MCU 从 0x8000 开始执行。从 0x8003 开始是中断向量表，当发生中断且中断使能后，PC 会跳转到对应的中断向量位置去执行。

### 3.2. XDATA

XDATA 共有 256 字节，地址为 0x300~0x3FF，可用于数据存储。

### 3.3. IDATA

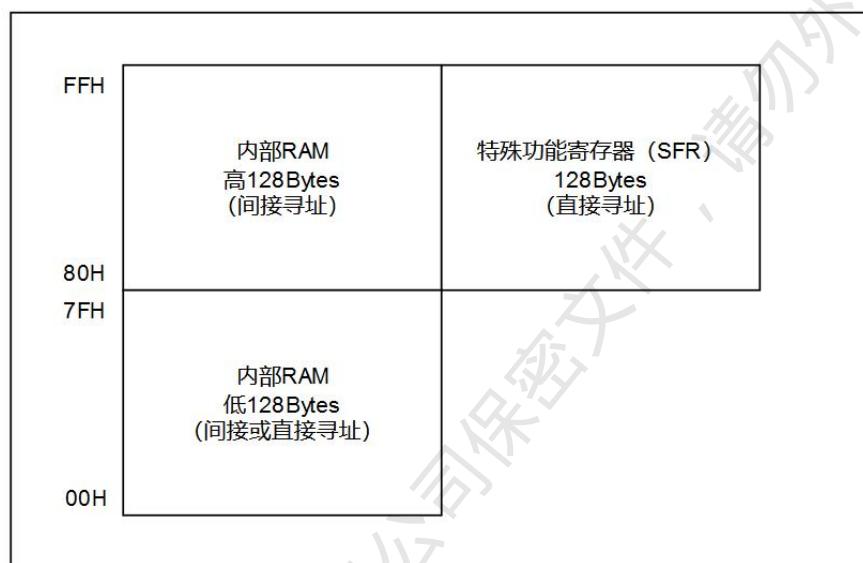

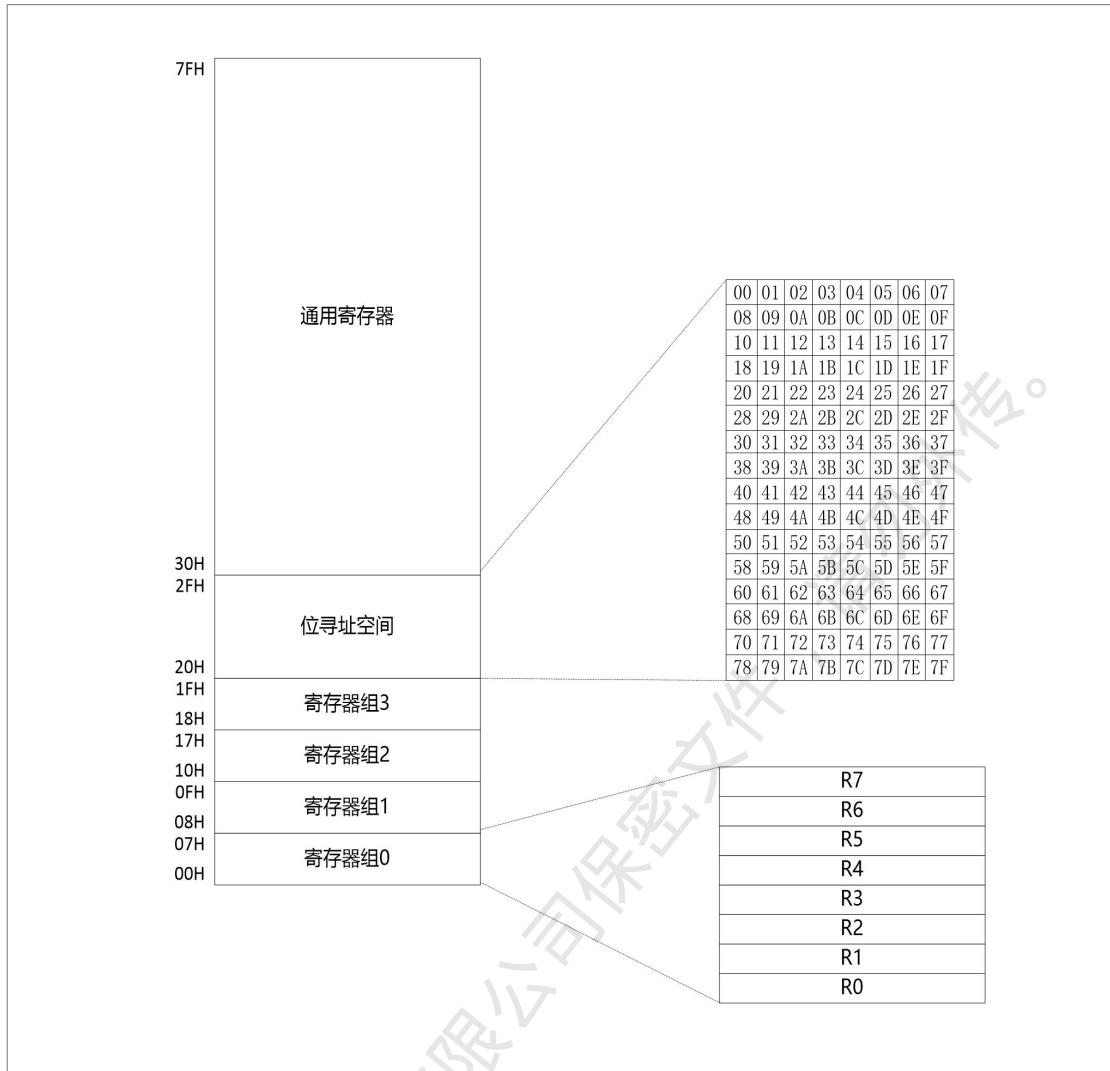

内部数据存储器空间大小为 256 字节。

内部数据存储器的地址空间的低 128 字节可以字节访问，高 128 字节和 SFR 共用一个地址空间，直接访问高 128 字节会访问到 SFR 空间，高 128 字节数据存储器只能通过间接寻址方式访问。

图 3-2 数据存储器

图 3-3 内部低 128 字节数据空间分配

### 3. 4. SFR 空间

|            | 0H/8H        | 1H/9H       | 2H/AH        | 3H/BH        | 4H/CH       | 5H/DH        | 6H/EH          | 7H/FH        |

|------------|--------------|-------------|--------------|--------------|-------------|--------------|----------------|--------------|

| <b>F8H</b> | UART0_BAUD0  | UART0_BAUD1 | UART0_DATA   | UART1_CON    | UART1_STA   | UART1_BAUD0  | UART1_BAUD1    | UART1_DATA   |

| <b>F0H</b> | B            | -           | -            | -            | -           | STMR_ALLCON  | UART0_CON      | UART0_STA    |

| <b>E8H</b> | STMR2_BRAKE  | STMR2_DTR   | STMR2_PCONRA | STMR2_PCONRB | STMR2_IE    | STMR2_SR     | ADK_CFG3       | -            |

| <b>E0H</b> | ACC          | STMR2_CMPAH | STMR2_CMBPL  | STMR2_CMPBH  | STMR2_CR    | STMR2_FCONR  | STMR2_VPERR    | STMR2_DTUA   |

| <b>D8H</b> | STMR1_PCONRB | STMR1_IE    | STMR1_SR     | STMR2_CNTL   | STMR2_CNTH  | STMR2_PRL    | STMR2_PRH      | STMR2_CMPAL  |

| <b>D0H</b> | PSW          | STMR1_CR    | STMR1_FCONR  | STMR1_VPERR  | STMR1_DTUA  | STMR1_BRAKE  | STMR1_DTR      | STMR1_PCONRA |

| <b>C8H</b> | STMR1_CNTL   | STMR1_CNTH  | STMR1_PRL    | STMR1_PRH    | STMR1_CMPAL | STMR1_CMPAH  | STMR1_CMBPL    | STMR1_CMPBH  |

| <b>C0H</b> | TMR2_CONL    | TMR2_CONH   | TMR2_CNTL    | TMR2_CNTH    | TMR2_PRL    | TMR2_PRH     | TMR2_PWML      | TMR2_PWMH    |

| <b>B8H</b> | IPO          | IP1         | LVD_CON0     | LVD_CON1     | LVD_CON2    | LVD_CON3     | LP_CON         | SYS_PND      |

| <b>B0H</b> | TMR1_CONL    | TMR1_CONH   | TMR1_CNTL    | TMR1_CNTH    | TMR1_PRL    | TMR1_PRH     | TMR1_PWML      | TMR1_PWMH    |

| <b>A8H</b> | IE0          | IE1         | FLASH_TRIM   | WKUP_CON0    | WKUP_PND    | WDT_CON      | WDT_KEY        | -            |

| <b>A0H</b> | FLASH_CON    | FLASH_STA   | FLASH_DATA   | FLASH_TIM0   | FLASH_TIM1  | FLASH_CRCLEN | FLASH_PASSWORD | FLASH_ADDR   |

| <b>98H</b> | -            | -           | -            | SPH          | PCON1       | -            | CRC_REG        | CRC_FIFO     |

| <b>90H</b> | P1           | -           | -            | -            | -           | -            | -              | -            |

| <b>88H</b> | TMRO_CONL    | TMRO_CONH   | TMRO_CNTL    | TMRO_CNTH    | TMRO_PRL    | TMRO_PRH     | TMRO_PWML      | TMRO_PWMH    |

| <b>80H</b> | P0           | SP          | DPL0         | DPH0         | DPL1        | DPH1         | DPS            | PCONO        |

## 4. 系统时钟

### 4.1. 时钟系统概述

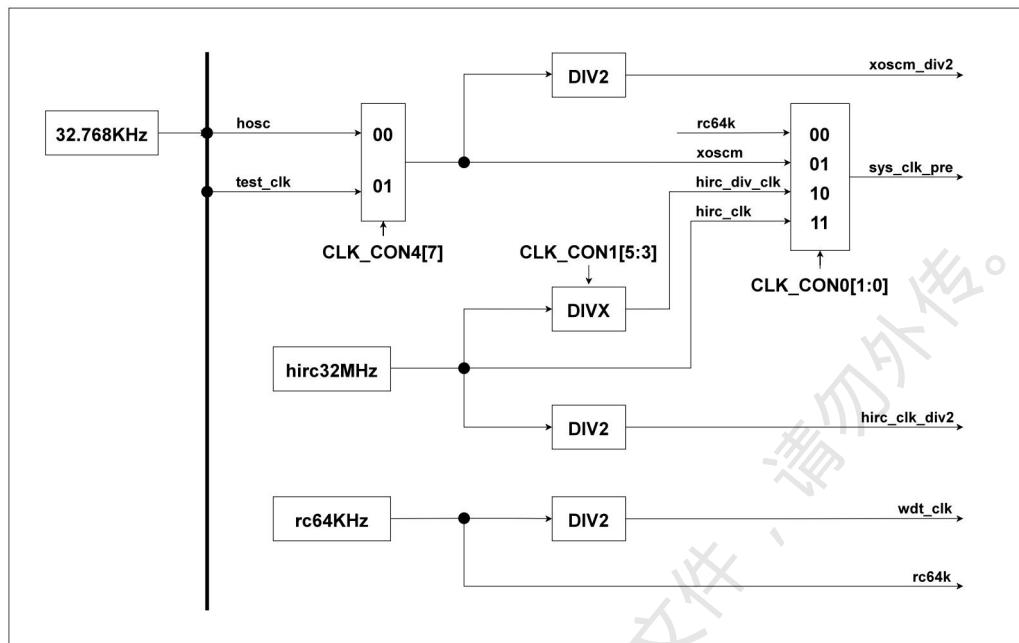

系统片上有一个 32MHz 的高速高精度 RC 振荡器，和一个外接的 32.768KHz 的低速晶体振荡器，以及内部 PMU 里面集成了一个 64KHz 的低速 RC 振荡器。

### 4.2. 时钟系统主要功能

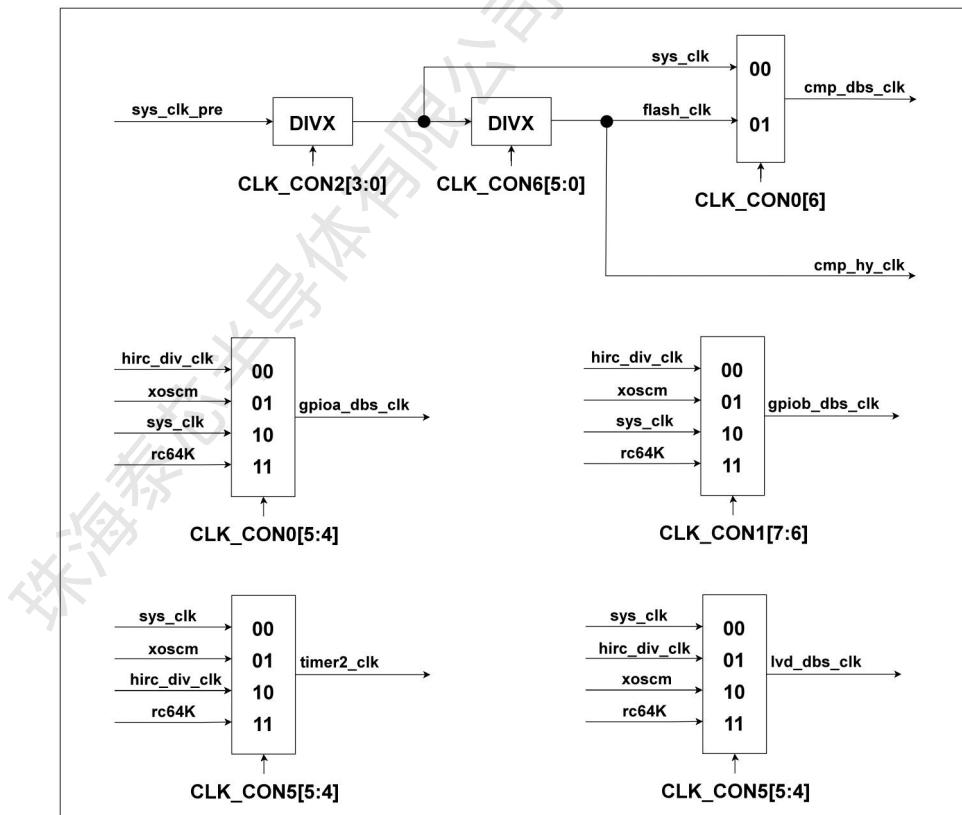

TX8W7010 芯片的时钟源来自于 3 个不同的时钟，分别是片外 32.768KHz 的低速晶振，片内 64K 低速 RC 和片内 32M 高速 RC。如图 4-1 所示，系统时钟可以通过 CLK\_CON0[1:0]对上述三个时钟源进行选择，选择后的时钟为芯片工作最快时钟（下文称为 sys\_clk\_pre）。如图 4-2 所示，sys\_clk\_pre 再经过 CLK\_CON2[3:0]进行分频，分频后时钟为系统时钟（下文称为 sys\_clk），系统中大部分外设与模数混合模块都将使用 sys\_clk，例如 UART、CRC16 等外设都使用 sys\_clk。如图 4-2 所示，GPIO 口的滤波时钟，Timer2 模块时钟和低电检测这几个特殊的模块会使用 sys\_clk，片外 32.768KHz 的低速晶振，片内 64K 低速 RC，片内 32M 高速 RC 分频后时钟进行选择。

### 4.3. 时钟系统框图

图 4-1 系统时钟框图

图 4-2 模块时钟框图

## 4.4. 系统振荡器

### 4.4.1. 内部低速 RC 振荡器

PMU 内部集成了一个 64KHz 的常开低速 RC 振荡器，当芯片上电时，系统工作在该 64KHz 的时钟，完成上电复位过程，等到系统复位释放以后才开始跑程序。

### 4.4.2. 内部高速 RC 振荡器

芯片内部集成了一个片上高速 RC 振荡器，支持最大 32MHz 的输出时钟给系统用，默认时关闭的，需要用户在程序中通过配置系统寄存器 AIP\_CON0[7]=1，打开高速 RC 振荡器，也可以通过配置 AIP\_CON0[7]=0，关闭该时钟源。注意在关闭该时钟前，系统需要先切换到低速 RC 振荡器。该高速 RC 振荡器可以通过量产过程中的校准程序校准，保证其精度满足应用方案需求。

### 4.4.3. 外部低速晶体振荡器

芯片内部集成了一个晶体振荡器启振电路，可以外部接一个低速 32.768KHz 的无源晶体振荡器，作为系统的工作时钟源。默认时关闭的，可以通过配置系统寄存器 AIP\_CON1[3]=1，打开该时钟源；也可以配置 AIP\_CON1[3]=0，关闭。

## 5. 复位系统

### 5.1. 上电复位

芯片上电的 POR 复位。

### 5.2. 掉电复位掉

芯片掉电的 BOR 复位。

### 5.3. 看门狗复位

芯片有一个独立于系统运行的看门狗模块，用于保护系统异常发生之后的复位重启系统。看门狗模块工作时钟是常开的 64KHz 的低速 RC 的 2 分频时钟，即工作在 32KHz 的独立于系统时钟的时钟。默认配置是 2 秒钟复位一次系统。所以在用户程序中需要在看门狗复位之前要喂狗，使其重新计时。用户可以配置看门狗复位时间间隔范围从 8ms ~ 262s，可以选择看门狗产生中断，不复位。中断和复位只能二选一。

#### 5.3.1. 控制寄存器列表

表 5-1 WDT 寄存器列表

| Address    | Register Name | Description      |

|------------|---------------|------------------|

| 0xAD (SFR) | WDT_CON       | WDT_CON register |

| 0xAE (SFR) | WDT_KEY       | WDT_KEY register |

### 5.3.2. 寄存器详细说明

#### 5.3.2.1. WDT\_CON

Addr = 0xAD (SFR)

| Bit(s) | Name   | Description                                                                                          | R/W | Reset |

|--------|--------|------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | WAKEEN | WDT 唤醒功能使能位<br>写 WDT_KEY=0xEE, 置位<br>写 WDT_KEY=0x22, 复位<br>0x0: 关闭<br>0x1: 打开                        | RO  | 0x0   |

| 6      | WDTPND | WDT 计数器计满标记位<br>写 WDT_KEY=0xAA, 清掉该标记位<br>0x0: 计数器未计满<br>0x1: 计数器计满                                  | RO  | 0x0   |

| 5      | INTEN  | WDT 中断功能使能位<br>写 WDT_KEY=0x5A, 置位<br>写 WDT_KEY=0xA5, 复位<br>0x1: 打开中断功能<br>0x0: 打开复位功能                | RO  | 0x0   |

| 4      | WDTE   | WDT 使能位<br>写 WDT_KEY=0xCC, 置位<br>写 WDT_KEY=0xDD, 复位<br>0x0: 关闭 watchdog 功能<br>0x1: 打开 watchdog 功能    | RW  | 0x1   |

| 3:0    | PSR    | 预分频系数<br>每次配置该位域之前必须先写 WDT_KEY=0x55<br>0x0: 不分频<br>0x1: 2 分频<br>0x2: 4 分频<br>0x3: 8 分频<br>0x4: 16 分频 | RW  | 0x8   |

|  |  |                                                                                                                                                                                                   |  |

|--|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|  |  | 0x5: 32 分频<br>0x6: 64 分频<br>0x7: 128 分频<br>0x8: 256 分频<br>0x9: 512 分频<br>0xA: 1024 分频<br>0xB: 2048 分频<br>0xC: 4096 分频<br>0xD: 8192 分频<br>0xE: 16384 分频<br>0xF: 32768 分频<br>看门狗复位时间=1/32K*256*分频系数 |  |

|--|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

### 5.3.2.2 WDT\_KEY

Addr = 0xAE (SFR)

| Bit(s) | Name    | Description                                                                                                                                                                                                                                                        | R/W | Reset |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7:0    | WDT_KEY | <b>喂狗数据寄存器</b><br>软件必须以一定的间隔写入 0xAA 完成喂狗操作，否则，当计数器为 0 时，看门狗会产生复位<br>当 pending 为 1 的时候，写入 0xAA 清除 pending<br>0x55: 表示允许访问和设置 wdt_psr<br>0xDD: 关闭看门狗<br>0xCC: 启动看门狗工作<br>0xAA: 喂狗并清除 wdt_pending<br>0xA5: 关闭中断<br>0x5A: 开启中断<br>0x22: 关闭 wake up<br>0xEE: 开启 wake up | W0  | 0x0   |

## 5.4. 低电检测复位

PMU 内部集成了低电压检测和过流检测功能电路，用于检测 PMU 供电部分异常情况，并可以把检测到低电压和过流等异常情况通过中断方式上报给 CPU 进行系统异常处理程序。另外低电压异常信号可以产生复位信号去复位系统，以免在低电压的情况下电路工作不正常而导致用户程序跑飞。低电压检测的阈值可以通过 LVD 控制寄存器设置。可以通过设置 LVD 控制寄存器对异常信号进行滤波去抖动，避免系统瞬态变化导致的正常电源压降而误发生意外低电复位系统的情况发生。

### 5.4.1. 控制寄存器列表

表 5-2 LVD 寄存器列表

| Address    | Register Name | Description       |

|------------|---------------|-------------------|

| 0xBA (SFR) | LVD_CON0      | LVD_CON0 register |

| 0xBB (SFR) | LVD_CON1      | LVD_CON1 register |

| 0xBC (SFR) | LVD_CON2      | LVD_CON2 register |

| 0xBD (SFR) | LVD_CON3      | LVD_CON3 register |

### 5.4.2. 寄存器详细说明

#### 5.4.2.1. LVD\_CON0

Addr = 0xBA (SFR)

| Bit(s) | Name  | Description         | R/W | Reset |

|--------|-------|---------------------|-----|-------|

| 7      | -     | -                   | -   | -     |

| 6      | LVDOE | LVD 中断和复位功能输出到系统使能位 | RW  | 0x1   |

|     |             |                                                                                                                                                              |    |     |

|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

|     |             | 0x0: 关闭<br>0x1: 打开<br><b>Note:</b> 使用 LVD 所有相关功能, 必须把 LVDOE 设置位 1.                                                                                           |    |     |

| 5   | LVDVDDRSTEN | LVD VDD 低电压复位功能使能位<br>0x0: 关闭<br>0x1: 打开                                                                                                                     | RW | 0x1 |

| 4   | LVDVCCRSTEN | LVD VCC 低电压复位功能使能位<br>0x0: 关闭<br>0x1: 打开                                                                                                                     | RW | 0x1 |

| 3:2 | PMULVD5SET  | VCC 电源电压低电检测阈值设置<br>0x0: 1.85/2.03V (掉电检测阈值/上电检测阈值)<br>0x1: 2.15/2.34V (掉电检测阈值/上电检测阈值)<br>0x2: 2.43/2.63V (掉电检测阈值/上电检测阈值)<br>0x3: 3.34/3.63V (掉电检测阈值/上电检测阈值) | RW | 0x0 |

| 1   | PMULVD15EN  | 1.5V 数字逻辑系统工作电压 VDD 低电检测功能使能位<br>0x0: 关闭<br>0x1: 打开                                                                                                          | RW | 0x1 |

| 0   | PMULVD5EN   | VCC 电源 VCC 电压低电检测功能使能位<br>0x0: 关闭<br>0x1: 打开                                                                                                                 | RW | 0x1 |

#### 5.4.2.2. LVD\_CON1

Addr = 0xBB (SFR)

| Bit(s) | Name     | Description                                              | R/W | Reset |

|--------|----------|----------------------------------------------------------|-----|-------|

| 7      | -        | -                                                        | -   | -     |

| 6      | VDDOCPND | VDD 过流检测标记位<br>写 1 清除标记位<br>0x0: VDD 没有过流<br>0x1: VDD 过流 | RW  | 0x0   |

|   |              |                                                          |    |     |

|---|--------------|----------------------------------------------------------|----|-----|

| 5 | LVDVDDPND    | VDD 低电检测标记位<br>写 1 清除标记位<br>0x0: VDD 没有低电<br>0x1: VDD 低电 | RW | 0x0 |

| 4 | LVDVCCPND    | VCC 低电检测标记位<br>写 1 清除标记位<br>0x0: VCC 没有低电<br>0x1: VCC 低电 | RW | 0x0 |

| 3 | LVDVCCSYNDIS | LVD VCC 低电检测同步器关闭位<br>0x0: 打开同步器<br>0x1: 关闭同步器           | RW | 0x1 |

| 2 | VDDOCBPSEN   | VDD 过流滤波去抖功能关闭位<br>0x0: 打开滤波器<br>0x1: 关闭滤波器              | RW | 0x1 |

| 1 | LVDVDDBPSEN  | VDD 低电滤波去抖功能关闭位<br>0x0: 打开滤波器<br>0x1: 关闭滤波器              | RW | 0x1 |

| 0 | LVDVCCBPSEN  | VCC 低电滤波去抖功能关闭位<br>0x0: 打开滤波器<br>0x1: 关闭滤波器              | RW | 0x1 |

#### 5.4.2.3. LVD\_CON2

Addr = 0xBC (SFR)

| Bit(s) | Name     | Description                                                                                                                                 | R/W | Reset |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | -        | -                                                                                                                                           | -   | -     |

| 6:0    | DBSHLMNT | LVD 低电和过流异常检测滤波器高电平滤波时钟周期设置数目<br><br><b>Note:</b> LVD 滤波时钟可以通过系统配置寄存器 CLKCON5[3:2]来选择。用户可以根据使用场景来选择滤波功能。滤波会导致异常发生到系统收到异常会有延迟时间，延迟时间会由设置的滤波的 | RW  | 0x2   |

|  |  |                                                                                                           |  |  |

|--|--|-----------------------------------------------------------------------------------------------------------|--|--|

|  |  | 时钟周期和配置滤波高电平和低电平滤波周期数目共同决定，设置的滤波时钟周期越长，滤波周期数目越多会导致该延迟越长。用户在使用时可以通过对该延迟的容忍度来合理配置。在有些对延迟比较敏感的应用场景可以关闭该滤波功能。 |  |  |

|--|--|-----------------------------------------------------------------------------------------------------------|--|--|

#### 5.4.2.4. LVD\_CON3

Addr = 0xBD (SFR)

| Bit(s) | Name    | Description                                                                                                                                                                                                                                   | R/W | Reset |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | -       | -                                                                                                                                                                                                                                             | -   | -     |

| 6:0    | DBSLLMT | LVD 低电和过流异常检测滤波器低电平滤波时钟周期设置数目<br><br>Note: LVD 滤波时钟可以通过系统配置寄存器 CLKCON5[3:2]来选择。用户可以根据使用场景来选择滤波功能。滤波会导致异常发生到系统收到异常会有延迟时间，延迟时间会由设置的滤波的时钟周期和配置滤波高电平和低电平滤波周期数目共同决定，设置的滤波时钟周期越长，滤波周期数目越多会导致该延迟越长。用户在使用时可以通过对该延迟的容忍度来合理配置。在有些对延迟比较敏感的应用场景可以关闭该滤波功能。 | RW  | 0x2   |

## 6. 低功耗管理

TX8W7010 芯片系统支持 3 个不同功耗等级的低功耗模式，从高到低依次是：Idle Mode、Stop Mode 和 Sleep Mode。其中功耗最低的是 Sleep 低功耗工作模式，该模式下常温整个芯片漏电可以低至 3uA。

## 6. 1. Idle Mode 及唤醒

通过配置系统寄存器 LP\_CON[7]=0，进入 Idle Mode。在 Idle 模式下只有 CPU 工作时钟被关闭，CPU 停止工作。通过中断方式唤醒 Idle Mode，唤醒之后会进入当前唤醒 Idle Mode 的中断服务子程序并执行。

## 6. 2. Stop Mode 及唤醒

通过配置系统寄存器 LP\_CON[1]=1，进入 Stop Mode。在 Stop 模式下系统时钟被关闭，CPU 及大部分系统时钟域的外设停止工作。通过选择多种唤醒源来唤醒 Stop Mode，唤醒源包括：所有 GPIO、比较器、基本 Timer2、看门狗、LVDVCC(电源的低电压检测信号)。Stop Mode 唤醒之后会继续跑后面的用户程序。

## 6. 3. Sleep Mode 及唤醒

通过配置系统寄存器 LP\_CON[0]=1，进入最低功耗的 Sleep Mode。在 Sleep 模式下系统时钟被关闭，CPU 及大部分系统时钟域的外设停止工作，除了 PMU 以外的模拟模块都要关闭，但是 XOSC 可选择开/关。通过选择多种唤醒源来唤醒 Sleep Mode，唤醒源包括：所有 GPIO 电平变换唤醒、基本 Timer2 定时中断唤醒、看门狗复位唤醒。Sleep Mode 唤醒之后可以通过进入 Sleep 模式之前配置的 LP\_CON[6]=1，会继续跑后面的用户程序，如果 LP\_CON[6]=0，则会复位系统重新跑用户程序。

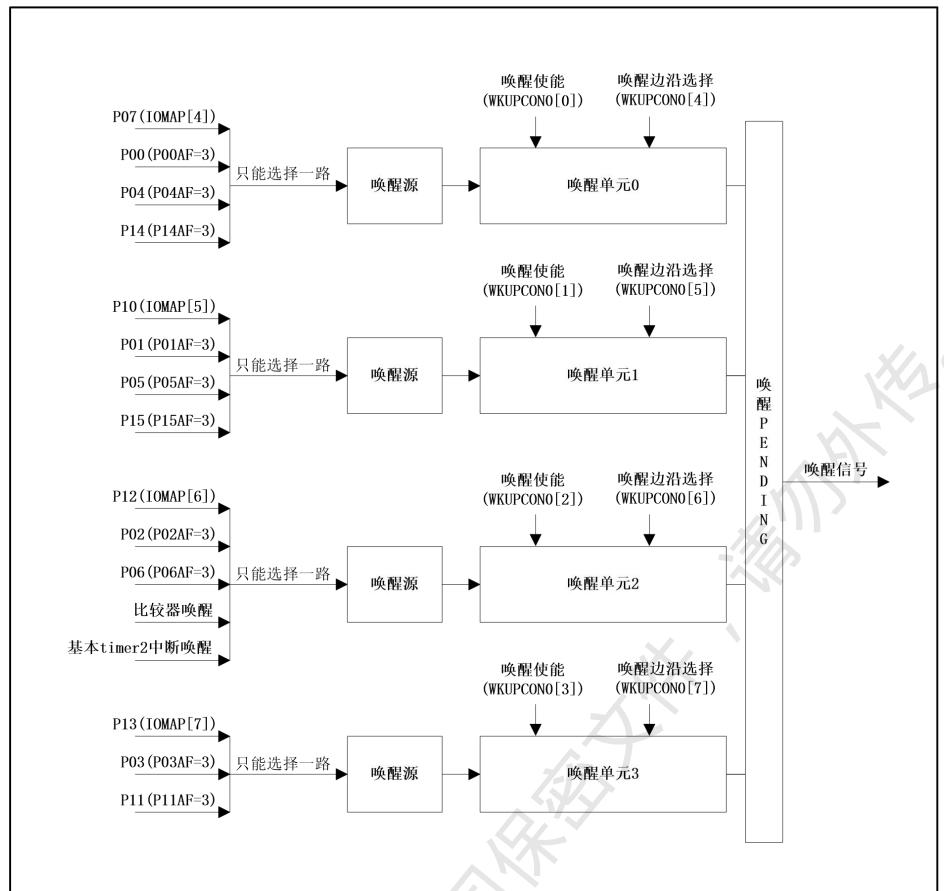

## 6. 4. 低功耗唤醒单元结构图

图 6-1 低功耗唤醒结构图

## 7. 系统控制模块

### 7.1. 功能概述

系统控制模块主要是用来管理和配置系统功能的，包括系统中模拟模块，时钟源，供电系统，时钟管理系统，低功耗及唤醒系统等系统功能配置。

### 7.2. 寄存器列表

表 7-1 系统寄存器列表

| Address     | Register Name | Description       |

|-------------|---------------|-------------------|

| 0x08 (XSFR) | SYS_CON0      | SYS_CON0 register |

|             |           |                    |

|-------------|-----------|--------------------|

| 0x09 (XSFR) | SYS_CON1  | SYS_CON1 register  |

| 0x0A (XSFR) | SYS_CON2  | SYS_CON2 register  |

| 0x0B (XSFR) | SYS_CON3  | SYS_CON3 register  |

| 0x0C (XSFR) | SYS_CON4  | SYS_CON4 register  |

| 0x0D (XSFR) | SYS_CON5  | SYS_CON5 register  |

| 0x10 (XSFR) | CLK_CON0  | CLK_CON0 register  |

| 0x11 (XSFR) | CLK_CON1  | CLK_CON1 register  |

| 0x12 (XSFR) | CLK_CON2  | CLK_CON2 register  |

| 0x13 (XSFR) | CLK_CON3  | CLK_CON3 register  |

| 0x14 (XSFR) | CLK_CON4  | CLK_CON4 register  |

| 0x15 (XSFR) | CLK_CON5  | CLK_CON5 register  |

| 0x16 (XSFR) | CLK_CON6  | CLK_CON6 register  |

| 0x28 (XSFR) | IO_MAP    | IO_MAP register    |

| 0x2A (XSFR) | IO_MAP1   | IO_MAP1 register   |

| 0x30 (XSFR) | AIP_CON0  | AIP_CON0 register  |

| 0x31 (XSFR) | AIP_CON1  | AIP_CON1 register  |

| 0x32 (XSFR) | AIP_CON2  | AIP_CON2 register  |

| 0x33 (XSFR) | AIP_CON3  | AIP_CON3 register  |

| 0x34 (XSFR) | AIP_CON4  | AIP_CON4 register  |

| 0xAB (SFR)  | WKUP_CON0 | WKUP_CON0 register |

| 0xAC (SFR)  | WKUP_PND  | WKUP_PND register  |

| 0xBE (SFR)  | LP_CON    | LP_CON register    |

| 0xBF (SFR)  | SYS_PND   | SYS_PND register   |

## 7.3. 寄存器详细说明

### 7.3.1. SYS\_CON0

Addr = 0x08 (XSFR)

| Bit(s) | Name         | Description                             | R/W | Reset |

|--------|--------------|-----------------------------------------|-----|-------|

| 7      | STMR1SOFTRST | 高级 Timer1 软复位<br>0x0: 软复位<br>0x1: 软复位释放 | RW  | 0x1   |

| 6      | TMR2SOFTRST  | 基本 Timer2 软复位<br>0x0: 软复位<br>0x1: 软复位释放 | RW  | 0x1   |

| 5      | TMR1SOFTRST  | 基本 Timer1 软复位<br>0x0: 软复位<br>0x1: 软复位释放 | RW  | 0x1   |

| 4      | TMROSOFTRST  | 基本 Timer0 软复位<br>0x0: 软复位<br>0x1: 软复位释放 | RW  | 0x1   |

| 3      | I2CSOFTRST   | I2C 软复位<br>0x0: 软复位<br>0x1: 软复位释放       | RW  | 0x1   |

| 2      | -            | -                                       | RW  | 0x1   |

| 1      | UART1SOFTRST | UART1 软复位<br>0x0: 软复位<br>0x1: 软复位释放     | RW  | 0x1   |

| 0      | UARTOSOFTRST | UART0 软复位<br>0x0: 软复位<br>0x1: 软复位释放     | RW  | 0x1   |

### 7.3.2. SYS\_CON1

Addr = 0x09 (XSFR)

| Bit(s) | Name        | Description                                                                                               | R/W | Reset |

|--------|-------------|-----------------------------------------------------------------------------------------------------------|-----|-------|

| 7:6    | MEMDVS[1:0] | 片上 SRAM 动态电压调整值<br><br>Note: 用户千万不要配置该寄存器，否则会导致芯片不确定行为！！！                                                 | RW  | 0x0   |

| 5      | FASTRSTEN   | 快速复位唤醒 Sleep Mode 使能<br><br>配置此功能主要是为了能在 sleep 低功耗模式下，设置通过复位唤醒 sleep 时，可以节省复位时间<br><br>0x0: 关闭<br>0x1: 打开 | RW  | 0x0   |

| 4      | GPIOSOFRST  | GPIO 模块软复位<br><br>0x0: 软复位<br>0x1: 软复位释放                                                                  | RW  | 0x1   |

| 3      | -           | -                                                                                                         | RW  | 0x1   |

| 2      | WDTSOFRST   | Watchdog 软复位<br><br>0x0: 软复位<br>0x1: 软复位释放                                                                | RW  | 0x1   |

| 1      | CRCSOFRST   | CRC 软复位<br><br>0x0: 软复位<br>0x1: 软复位释放                                                                     | RW  | 0x1   |

| 0      | STMR2SOFRST | 高级 Timer2 软复位<br><br>0x0: 软复位<br>0x1: 软复位释放                                                               | RW  | 0x1   |

### 7.3.3. SYS\_CON2

Addr = 0x0A (XSFR)

| Bit(s) | Name          | Description                                         | R/W | Reset |

|--------|---------------|-----------------------------------------------------|-----|-------|

| 7      | -             | -                                                   | RW  | 0x0   |

| 6      | TMR2SWSYNCBPS | 基础 Timer2 软件同步 bypass 使能位<br><br>0x0: 关闭<br>0x1: 打开 | RW  | 0x1   |

|   |             |                                                                                                          |    |     |

|---|-------------|----------------------------------------------------------------------------------------------------------|----|-----|

| 5 | IODBSSOFRST | I0 debouce 模块软复位<br>0x0: 软复位<br>0x1: 软复位释放                                                               | RW | 0x1 |

| 4 | -           | -                                                                                                        | -  | -   |

| 3 | TMR22IREN   | 基本 Timer2 与高级 Timer2 联合完成红外发送功能使能位<br>基本 Timer2 作为载波 PWM, 高级 Timer2 通道 A 作为调制波 PWM<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 2 | ISDWDTRSTEN | ISD 调试模式下 WDT 复位功能使能位<br>0x0: 关闭<br>0x1: 打开                                                              | RW | 0x0 |

| 1 | -           | -                                                                                                        | -  | -   |

| 0 | LVDVCCWKEN  | LVDVCC 唤醒使能位<br>0x0: 关闭<br>0x1: 打开                                                                       | RW | 0x0 |

**Note:** SYS\_CON2 寄存器中保留位用于特殊测试功能, 用户程序不能随意写操作, 可能会带来系统风险!

#### 7.3.4. SYS\_CON3

Addr = 0x0B (XSFR)

| Bit(s) | Name      | Description                                                                                                                            | R/W | Reset |

|--------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7:6    | EXTSLPCNT | 低功耗 Sleep Mode 流程退出低功耗 LDO 延迟的时间配置<br>低功耗模式进入之前必须将系统时钟切换成低速的 64KHz 的 RC, 所以延迟时间=n*T64k<br>0x0: 1 个系统周期<br>0x1: 2 个系统周期<br>0x2: 3 个系统周期 | RW  | 0x0   |

|     |             |                                                                                                                                                                                       |    |     |

|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

|     |             | 0x3: 4 个系统周期 (推荐配置)                                                                                                                                                                   |    |     |

| 5:4 | CMPUPCNT    | <p>低功耗 Sleep Mode 流程退出低功耗流程中打开程序存储器供电的延迟时间配置</p> <p>低功耗模式进入之前必须将系统时钟切换成低速的 64KHz 的 RC，所以延迟时间=n*T64k</p> <p>0x0: 1 个系统周期<br/>0x1: 2 个系统周期<br/>0x2: 3 个系统周期<br/>0x3: 4 个系统周期 (推荐配置)</p> | RW | 0x0 |

| 3:2 | OPMLDOCNT   | <p>低功耗 Sleep Mode 流程打开主 LDO 延迟时间配置</p> <p>低功耗模式进入之前必须将系统时钟切换成低速的 64KHz 的 RC，所以延迟时间=n*T64k</p> <p>0x0: 1 个系统周期<br/>0x1: 2 个系统周期<br/>0x2: 3 个系统周期<br/>0x3: 4 个系统周期 (推荐配置)</p>           | RW | 0x0 |

| 1:0 | CLSMMLDOCNT | <p>低功耗 Sleep Mode 流程关闭主 LDO 延迟时间配置</p> <p>低功耗模式进入之前必须将系统时钟切换成低速的 64KHz 的 RC，所以延迟时间=n*T64k</p> <p>0x0: 1 个系统周期<br/>0x1: 2 个系统周期<br/>0x2: 3 个系统周期<br/>0x3: 4 个系统周期 (推荐配置)</p>           | RW | 0x0 |

### 7.3.5. SYS\_CON4

Addr = 0x0C (XSFR)

| Bit(s) | Name     | Description                                     | R/W | Reset |

|--------|----------|-------------------------------------------------|-----|-------|

| 7      | P07DBSEN | <p>P07 输入滤波功能使能位</p> <p>0x0: 关闭<br/>0x1: 打开</p> | RW  | 0x0   |

| 6      | P06DBSEN | <p>P06 输入滤波功能使能位</p> <p>0x0: 关闭</p>             | RW  | 0x0   |

|   |          |                                     |    |     |

|---|----------|-------------------------------------|----|-----|

|   |          | 0x1: 打开                             |    |     |

| 5 | P05DBSEN | P05 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 4 | P04DBSEN | P04 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 3 | P03DBSEN | P03 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 2 | P02DBSEN | P02 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 1 | P01DBSEN | P01 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 0 | P00DBSEN | P00 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

### 7.3.6. SYS\_CON5

Addr = 0x0D (XSFR)

| Bit(s) | Name     | Description                         | R/W | Reset |

|--------|----------|-------------------------------------|-----|-------|

| 7:6    | -        | -                                   | -   | -     |

| 5      | P15DBSEN | P15 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW  | 0x0   |

| 4      | P14DBSEN | P14 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW  | 0x0   |

|   |          |                                     |    |     |

|---|----------|-------------------------------------|----|-----|

| 3 | P13DBSEN | P13 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 2 | P12DBSEN | P12 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 1 | P11DBSEN | P11 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 0 | P10DBSEN | P10 输入滤波功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

### 7.3.7. CLK\_CON0

Addr = 0x10 (XSFR)

| Bit(s) | Name        | Description                                                                             | R/W | Reset |

|--------|-------------|-----------------------------------------------------------------------------------------|-----|-------|

| 7      | -           | -                                                                                       | -   | -     |

| 6      | CMPDBSSEL   | 比较器滤波时钟选择位<br>0x0: 选择 eflash_clk<br>0x1: 选择 sys_clk                                     | RW  | 0x0   |

| 5:4    | PODBSCLKSEL | P0 滤波时钟选择位<br>0x0: 选择 hirc_div_clk<br>0x1: 选择 xoscm<br>0x2: 选择 sys_clk<br>0x3: 选择 rc64k | RW  | 0x0   |

| 3:2    | CLKTOIOSEL  | I0 输出时钟源选择位<br>0x0: 选择 sys_clk<br>0x1: 选择 hirc_div_clk<br>0x2: 选择 lirc<br>0x3: 选择 xoscm | RW  | 0x0   |

| 1:0    | SYSCLKSEL   | 系统时钟选择位                                                                                 | RW  | 0x0   |

|  |  |                                                                            |  |  |

|--|--|----------------------------------------------------------------------------|--|--|

|  |  | 0x0: 选择 rc64k<br>0x1: 选择 xoscm<br>0x2: 选择 hirc_div_clk<br>0x3: 选择 hirc_clk |  |  |

|--|--|----------------------------------------------------------------------------|--|--|

### 7.3.8. CLK\_CON1

Addr = 0x11 (XSFR)

| Bit(s) | Name        | Description                                                                                                     | R/W | Reset |

|--------|-------------|-----------------------------------------------------------------------------------------------------------------|-----|-------|

| 7:6    | P1DBSCLKSEL | P1 滤波时钟选择位<br><br>0x0: 选择 hirc_div_clk<br>0x1: 选择 xoscm<br>0x2: 选择 sys_clk<br>0x3: 选择 rc64k                     | RW  | 0x0   |

| 5:3    | HIRCCLKDIV  | 高速 HRCOSC 时钟源分频设置<br><br>配置比为 n+1 时钟<br><br>0x0: 不分频<br>0x1: 2 分频<br>0x2: 3 分频<br>.....<br>0x6: 7 分频<br>0x7: 关闭 | RW  | 0x6   |

| 2:0    | CLKTOIODIV  | I0 输出时钟源分频设置<br><br>配置比为 n+1 时钟<br><br>0x0: 不分频<br>0x1: 2 分频<br>0x2: 3 分频<br>.....<br>0x6: 7 分频<br>0x7: 关闭      | RW  | 0x0   |

### 7.3.9. CLK\_CON2

Addr = 0x12 (XSFR)

| Bit(s) | Name      | Description                                                                                     | R/W | Reset |

|--------|-----------|-------------------------------------------------------------------------------------------------|-----|-------|

| 7:4    | -         | -                                                                                               | -   | -     |

| 3:0    | SYSCLKDIV | 系统时钟分频设置<br>配置比为 n+1 时钟<br>0x0: 不分频<br>0x1: 2 分频<br>0x2: 3 分频<br>.....<br>0xE: 15 分频<br>0xF: 关闭 | RW  | 0x0   |

### 7.3.10. CLK\_CON3

Addr = 0x13 (XSFR)

| Bit(s) | Name      | Description                                 | R/W | Reset |

|--------|-----------|---------------------------------------------|-----|-------|

| 7      | TMR2CLKEN | 基本 Timer2 模块时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW  | 0x1   |

| 6      | TMR1CLKEN | 基本 Timer1 模块时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW  | 0x1   |

| 5      | TMROCLKEN | 基本 Timer0 模块时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW  | 0x1   |

| 4      | CRCCLKEN  | CRC 模块时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟       | RW  | 0x1   |

| 3      | I2CCLKEN  | I2C 模块时钟使能位<br>0x0: 关闭时钟                    | RW  | 0x1   |

|   |            |                                                |    |     |

|---|------------|------------------------------------------------|----|-----|

|   |            | 0x1: 打开时钟                                      |    |     |

| 2 | -          | -                                              | RW | 0x1 |

| 1 | UART1CLKEN | <b>UART1 模块时钟使能位</b><br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW | 0x1 |

| 0 | UARTOCLKEN | <b>UART0 模块时钟使能位</b><br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW | 0x1 |

### 7.3.11. CLK\_CON4

Addr = 0x14 (XSFR)

| Bit(s) | Name        | Description                                 | R/W | Reset |

|--------|-------------|---------------------------------------------|-----|-------|

| 7      | TESTCLKEN   | 测试时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟           | RW  | 0x0   |

| 6      | -           | -                                           | -   | -     |

| 5      | RAMCLKEN    | 片上 SRAM 时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟     | RW  | 0x1   |

| 4      | CMPDBSCLKEN | 比较器 debouce 时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW  | 0x1   |

| 3:2    | -           | -                                           | -   | -     |

| 1      | STMR2CLKEN  | 高级 Timer2 模块时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW  | 0x1   |

| 0      | STMR1CLKEN  | 高级 Timer1 模块时钟使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟 | RW  | 0x1   |

### 7.3.12. CLK\_CON5

Addr = 0x15 (XSFR)

| Bit(s) | Name         | Description                                                                                    | R/W | Reset |

|--------|--------------|------------------------------------------------------------------------------------------------|-----|-------|

| 7:6    | -            | -                                                                                              | -   | -     |

| 5:4    | TMR2CLKSEL   | 基本 Timer2 模块时钟选择位<br>0x0: 选择 sys_clk<br>0x1: 选择 xoscm<br>0x2: 选择 hirc_div_clk<br>0x3: 选择 rc64k | RW  | 0x0   |

| 3:2    | LVDDBSCLKSEL | LVD 模块滤波时钟源选择位<br>0x0: 选择 sys_clk<br>0x1: 选择 hirc_div_clk<br>0x2: 选择 xoscm<br>0x3: 选择 rc64k    | RW  | 0x0   |

| 1      | -            | -                                                                                              | -   | -     |

| 0      | TCLKEN       | 测试时钟 1 使能位<br>0x0: 关闭时钟<br>0x1: 打开时钟                                                           | RW  | 0x1   |

### 7.3.13. CLK\_CON6

Addr = 0x16 (XSFR)

| Bit(s) | Name    | Description                                                                                 | R/W | Reset |

|--------|---------|---------------------------------------------------------------------------------------------|-----|-------|

| 7:6    | -       | -                                                                                           | -   | -     |

| 5:0    | MCLKDIV | 存储器烧写时钟分频设置<br>配置比为 n+1 时钟<br>0x00: 不分频<br>0x01: 2 分频<br>0x02: 3 分频<br>.....<br>0x3E: 63 分频 | RW  | 0x0   |

|  |  |          |  |  |

|--|--|----------|--|--|

|  |  | 0x3F: 关闭 |  |  |

|--|--|----------|--|--|

### 7.3.14. AIP\_CON0

Addr = 0x30 (XSFR)

| Bit(s) | Name  | Description                                              | R/W | Reset |

|--------|-------|----------------------------------------------------------|-----|-------|

| 7      | HRCEN | HRC 时钟使能信号<br>0x0: 关闭<br>0x1: 打开                         | RW  | 0x0   |

| 6:0    | HRCSC | HRC 时钟频率细调 (step=1%)<br>0x00: low<br>.....<br>0x7F: high | RW  | 0x48  |

### 7.3.15. AIP\_CON1

Addr = 0x31 (XSFR)

| Bit(s) | Name           | Description                                                    | R/W | Reset |

|--------|----------------|----------------------------------------------------------------|-----|-------|

| 7      | -              | -                                                              | -   | -     |

| 6:5    | HRCSCADD_B2TQ1 | HRC 时钟频率细调的高 2 位 (step=0.5%)<br>0x0: low<br>.....<br>0x3: high | RW  | 0x1   |

| 4      | HRCTESTEN      | HRC 内部模拟电压测试使能信号<br>0x0: 关闭<br>0x1: 打开                         | RW  | 0x0   |

| 3      | XOSCEN         | 晶振的使能信号<br>0x0: 关闭<br>0x1: 打开                                  | RW  | 0x0   |

| 2      | XOSCHY         | 输出时钟迟滞窗口选择<br>0x0: 没有迟滞<br>0x1: 有+-10%的迟滞                      | RW  | 0x1   |

|   |             |                                        |    |     |

|---|-------------|----------------------------------------|----|-----|

| 1 | HRCSCADD_B0 | HRC 时钟频率细调的低 1 位 (step=0.5%)           | RW | 0x0 |

| 0 | HRCMR       | HRC 时钟频率粗调<br>0x0: 16MHz<br>0x1: 32MHz | RW | 0x1 |

### 7.3.16. AIP\_CON2

Addr = 0x32 (XSFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:0    | -    | -           | RW  | 0x0   |

### 7.3.17. AIP\_CON3

Addr = 0x33 (XSFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:0    | -    | -           | RW  | 0x0   |

### 7.3.18. AIP\_CON4

Addr = 0x34 (XSFR)

| Bit(s) | Name | Description | R/W | Reset |

|--------|------|-------------|-----|-------|

| 7:0    | -    | -           | -   | -     |

### 7.3.19. IO\_MAP

Addr = 0x28 (XSFR)

| Bit(s) | Name    | Description                                            | R/W | Reset |

|--------|---------|--------------------------------------------------------|-----|-------|

| 7      | WKUPIN3 | GPIO wakeup 通道 3 输入引脚选择<br>0x0: 不选择 P13<br>0x1: 选择 P13 | RW  | 0x0   |

|     |            |                                                                                                                                  |    |     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 6   | WKUPIN2    | GPIO wakeup 通道 2 输入引脚选择<br>0x0: 不选择 P12<br>0x1: 选择 P12                                                                           | RW | 0x0 |

| 5   | WKUPIN1    | GPIO wakeup 通道 1 输入引脚选择<br>0x0: 不选择 P10<br>0x1: 选择 P10                                                                           | RW | 0x0 |

| 4   | WKUPINO    | GPIO wakeup 通道 0 输入引脚选择<br>0x0: 不选择 P07<br>0x1: 选择 P07                                                                           | RW | 0x0 |

| 3:2 | CLKTOIOMAP | IO 输出时钟源功能 pin 脚选择位<br>0x0: 关闭 IO 输出时钟功能<br>0x1: 选择 P04 输出时钟<br>0x2: 选择 P05 输出时钟<br>0x3: 选择 P12 输出时钟                             | RW | 0x0 |

| 1:0 | ISPMAP     | 烧写/调试 pin 脚选择位<br>0x0: 关闭烧写/调试功能<br>0x1: 选择 P10【ISP_CLK】 , P07【ISP_DAT】<br>0x2: 选择 P00【ISP_CLK】 , P01【ISP_DAT】<br>0x3: 关闭烧写/调试功能 | RW | 0x1 |

### 7.3.20. IO\_MAP1

Addr = 0x2A (XSFR)

| Bit(s) | Name        | Description                                                          | R/W | Reset |

|--------|-------------|----------------------------------------------------------------------|-----|-------|

| 7      | MEMDVSE     | 片上 SRAM 动态电压调整值使能位<br><br><b>Note:</b> 用户千万不要配置该寄存器，否则会导致芯片不确定行为！！！！ | RW  | 0x0   |

| 6:5    | MEMDVS[3:2] | 片上 SRAM 动态电压调整值<br><br><b>Note:</b> 用户千万不要配置该寄存器，否则会导致芯片不确定行为！！！！    | RW  | 0x0   |

| 4      | RSTBEN      | RSTB 复位功能使能位<br>0x0: 关闭 RSTB 复位功能<br>0x1: 打开 RSTB 复位功能               | RW  | 0x0   |

|     |         |                                                                                                                                                                   |    |     |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 3:2 | MPDNCNT | 低功耗 Sleep Mode 流程进入关闭程序存储器供电的延迟时间配置<br><br>低功耗模式进入之前必须将系统时钟切换成低速的 64KHz 的 RC，所以延迟时间=n*T64k。<br>0x0: 1 个系统周期<br>0x1: 2 个系统周期<br>0x2: 3 个系统周期<br>0x3: 4 个系统周期（推荐配置） | RW | 0x0 |

| 1:0 | -       | -                                                                                                                                                                 | RW | 0x0 |

### 7.3.21. WKUP\_CON0

Addr = 0xAB (SFR)

| Bit(s) | Name     | Description                                                | R/W | Reset |

|--------|----------|------------------------------------------------------------|-----|-------|

| 7      | WKUP3EDG | 低功耗模式 wakeup 通道 3 输入触发边沿设置<br>0x0: 上升沿触发唤醒<br>0x1: 下降沿触发唤醒 | RW  | 0x0   |

| 6      | WKUP2EDG | 低功耗模式 wakeup 通道 2 输入触发边沿设置<br>0x0: 上升沿触发唤醒<br>0x1: 下降沿触发唤醒 | RW  | 0x0   |

| 5      | WKUP1EDG | 低功耗模式 wakeup 通道 1 输入触发边沿设置<br>0x0: 上升沿触发唤醒<br>0x1: 下降沿触发唤醒 | RW  | 0x0   |

| 4      | WKUPOEDG | 低功耗模式 wakeup 通道 0 输入触发边沿设置<br>0x0: 上升沿触发唤醒<br>0x1: 下降沿触发唤醒 | RW  | 0x0   |

| 3      | WKUP3EN  | 低功耗模式 wakeup 通道 3 功能使能位<br>0x0: 关闭<br>0x1: 打开              | RW  | 0x0   |

| 2      | WKUP2EN  | 低功耗模式 wakeup 通道 2 功能使能位<br>0x0: 关闭<br>0x1: 打开              | RW  | 0x0   |

|   |         |                                               |    |     |

|---|---------|-----------------------------------------------|----|-----|

| 1 | WKUP1EN | 低功耗模式 wakeup 通道 1 功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

| 0 | WKUPOEN | 低功耗模式 wakeup 通道 0 功能使能位<br>0x0: 关闭<br>0x1: 打开 | RW | 0x0 |

### 7.3.22. WKUP\_PND

Addr = 0xAC (SFR)

| Bit(s) | Name      | Description                                                        | R/W | Reset |

|--------|-----------|--------------------------------------------------------------------|-----|-------|

| 7      | WKUP3PCLR | 低功耗模式 wakeup 通道 3 清 pending 位<br>0x0: 无操作<br>0x1: 清 pending        | RW  | 0x0   |

| 6      | WKUP2PCLR | 低功耗模式 wakeup 通道 2 清 pending 位<br>0x0: 无操作<br>0x1: 清 pending        | RW  | 0x0   |

| 5      | WKUP1PCLR | 低功耗模式 wakeup 通道 1 清 pending 位<br>0x0: 无操作<br>0x1: 清 pending        | RW  | 0x0   |

| 4      | WKUPOPCLR | 低功耗模式 wakeup 通道 0 清 pending 位<br>0x0: 无操作<br>0x1: 清 pending        | RW  | 0x0   |

| 3      | WKUP3PND  | 低功耗模式 wakeup 通道 3 唤醒 pending 位<br>0x0: 无 pending<br>0x1: 有 pending | RW  | 0x0   |

| 2      | WKUP2PND  | 低功耗模式 wakeup 通道 2 唤醒 pending 位<br>0x0: 无 pending<br>0x1: 有 pending | RW  | 0x0   |

| 1      | WKUP1PND  | 低功耗模式 wakeup 通道 1 唤醒 pending 位<br>0x0: 无 pending<br>0x1: 有 pending | RW  | 0x0   |

| 0      | WKUPOPND  | 低功耗模式 wakeup 通道 0 唤醒 pending 位                                     | RW  | 0x0   |

|  |  |                                  |  |  |

|--|--|----------------------------------|--|--|

|  |  | 0x0: 无 pending<br>0x1: 有 pending |  |  |

|--|--|----------------------------------|--|--|

### 7.3.23. LP\_CON

Addr = 0xBE (SFR)

| Bit(s) | Name      | Description                                                                                                                                                                                                                                   | R/W | Reset |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|

| 7      | IDLE      | <b>Idle 低功耗模式使能</b><br>0x0: 关闭<br>0x1: 打开, 进入 Idle 低功耗模式                                                                                                                                                                                      | RW  | 0x1   |

| 6      | SLEEPGOEN | <b>Sleep 低功耗模式唤醒后继续跑后续程序使能位</b><br>0x0: Sleep 模式唤醒后复位重新跑程序<br>0x1: Sleep 模式唤醒后继续跑后续程序                                                                                                                                                         | RW  | 0x1   |

| 5      | CPDIS     | <b>用户程序保护功能关闭位</b><br>CPU 和 ISD 都无法写寄存器<br>0x0: 打开 (默认状态)<br>0x1: 关闭                                                                                                                                                                          | RO  | 0x0   |

| 4      | LPGLIRCEN | <b>低功耗进入低速 RC 选择</b><br>低功耗 Sleep 模式下, 可以通过配置该寄存器为 1, 在系统进入 Sleep 模式后自动 gate 住 RC64K 低速时钟, 目的是减少 Sleep 的漏电功耗。也可以选择不关闭 RC64K.<br><b>Note:</b> 该功能只能在 Sleep 低功耗模式下, 由 GPIO 唤醒系统的场景下才能使用该功能。如果是 TIMER2 定时唤醒场景下不可以关闭该时钟, 造成 TIMER2 没有工作时钟而不能唤醒系统。 | RW  | 0x0   |

| 3      | CMCEDIS   | <b>程序存储器空片硬件自动检查功能关闭位</b><br>默认芯片上电以后会自动检查程序存储器是否有烧写程序, 如果没有烧写程序, 则 hold 住 cpu 不跑任何程序。<br>0x0: 开启空片自动检查功能<br>0x1: 关闭空片自动检查功能                                                                                                                  | RW  | 0x0   |

| 2      | TMHCPU    | <b>测试模式下 hold 住 CPU 使能</b>                                                                                                                                                                                                                    | RW  | 0x0   |

|   |       |                                                                                 |    |     |

|---|-------|---------------------------------------------------------------------------------|----|-----|

|   |       | <b>Note:</b> 用户程序不要随便写这个寄存器，会造成系统功能异常的风险！！！<br>0x0: 不 hold CPU<br>0x1: hold CPU |    |     |

| 1 | STOP  | Stop 低功耗模式使能<br>0x0: 关闭<br>0x1: 打开，进入 Stop 低功耗模式                                | RW | 0x0 |

| 0 | SLEEP | Sleep 低功耗模式使能<br>0x0: 关闭<br>0x1: 打开，进入 Sleep 低功耗模式                              | RW | 0x0 |

### 7.3.24. SYS\_PND

Addr = 0xBF (SFR)

| Bit(s) | Name      | Description            | R/W | Reset |

|--------|-----------|------------------------|-----|-------|

| 7:6    | -         | -                      | -   | -     |

| 5      | SLPSTACLR | 写 1 清掉系统 sleep 标志位     | RW  | 0x0   |

| 4      | SFTRSTCLR | 写 1 清掉系统软复位标志位         | RW  | 0x0   |

| 3:2    | -         | -                      | -   | -     |

| 1      | SLPPND    | 系统 sleep 标志位           | RW  | 0x0   |

| 0      | SFTRSTPND | 系统软复位标志位<br>写 1 系统软复位。 | RW  | 0x0   |

## 8. 中断系统

### 8.1. 中断概述

TX8W7010 支持多达 14 个中断源。每个中断源都有独立的中断使能信号，可以通过软件来控制其使能开关。中断控制器有以下特性：

- 从 14 个中断源接收中断

- 每个中断有固定的中断号，中断号越小优先级越高

- 中断延时：5~8 机器周期

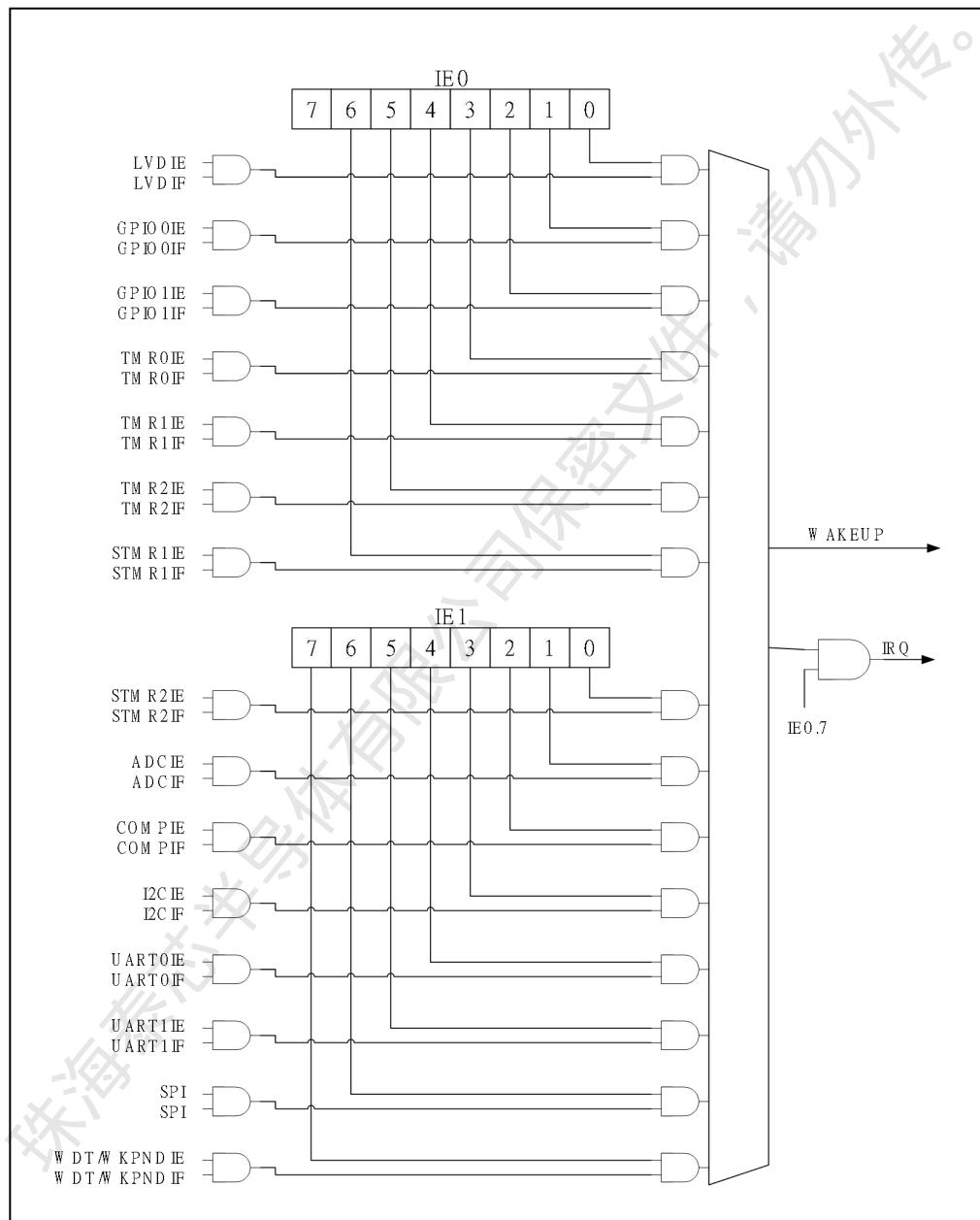

## 8.2. 结构框图

图 8-1 中断结构图

### 8.3. 中断向量表

中断控制器支持 14 个中断源。当中断发生且中断使能之后，跳转到对应向量地址去执行 LCALL 指令来进入中断服务程序。

表 8-1 中断向量表

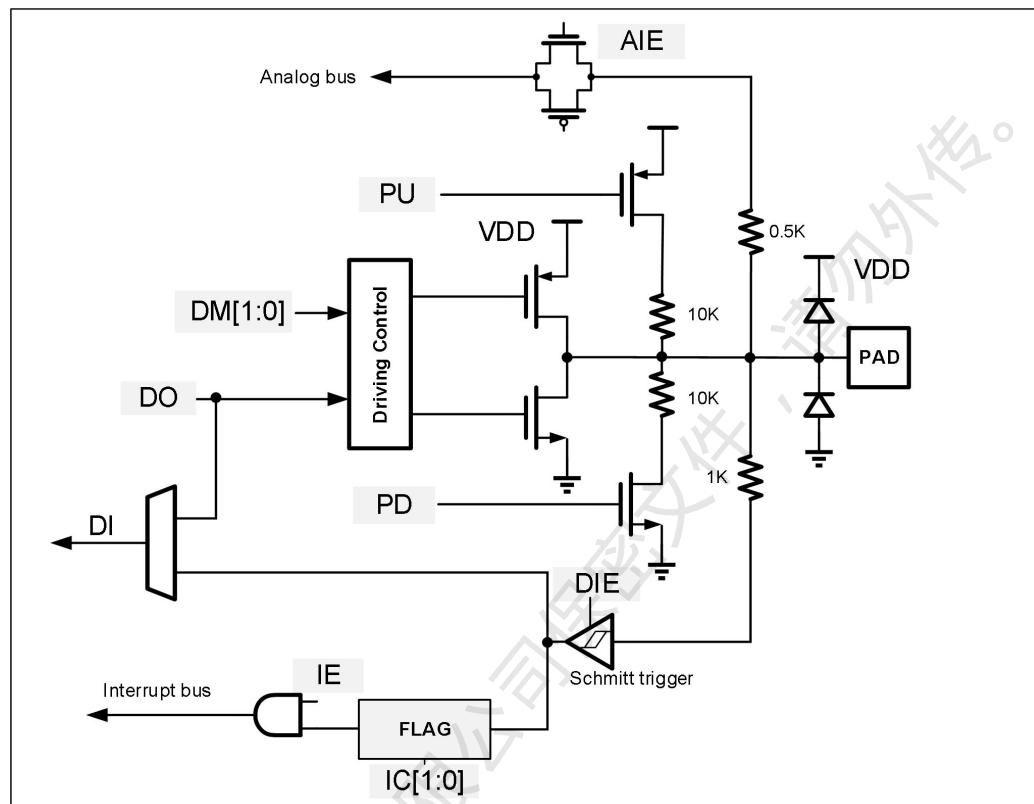

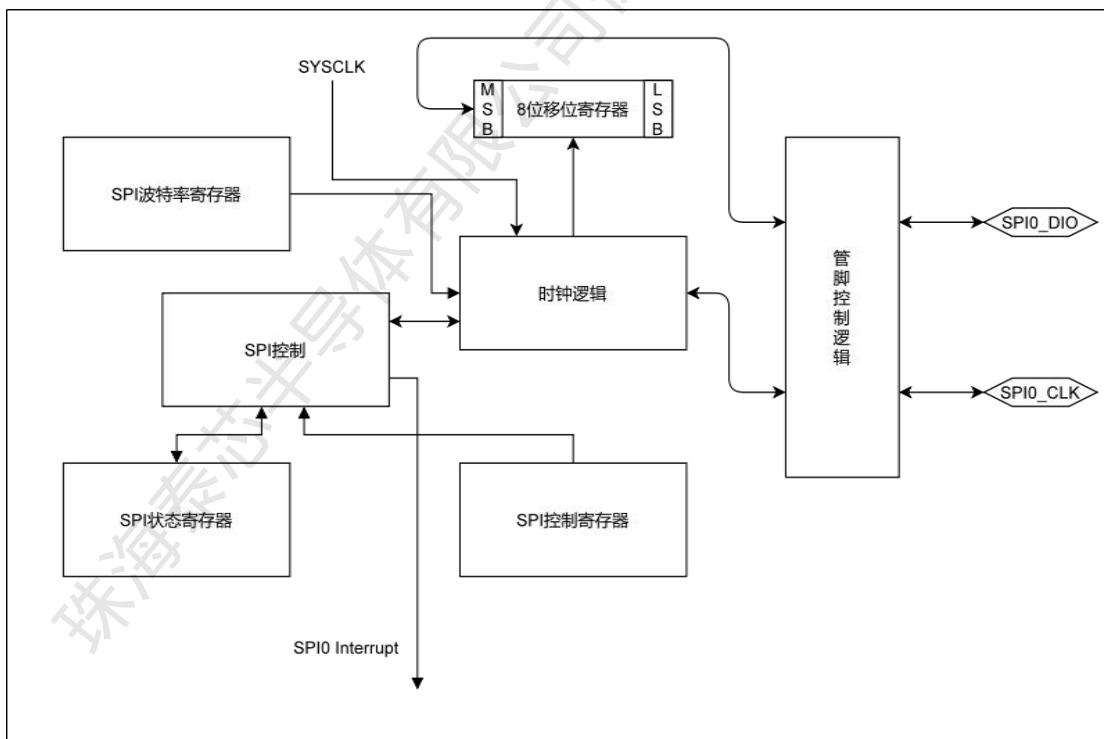

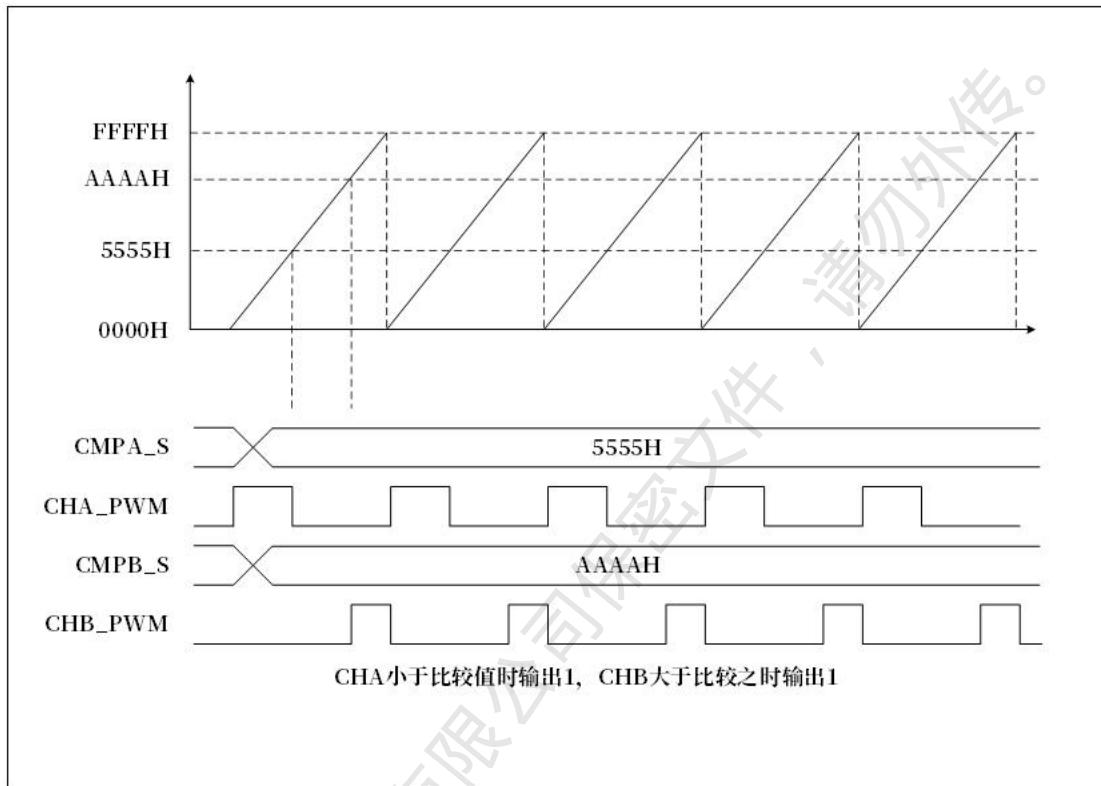

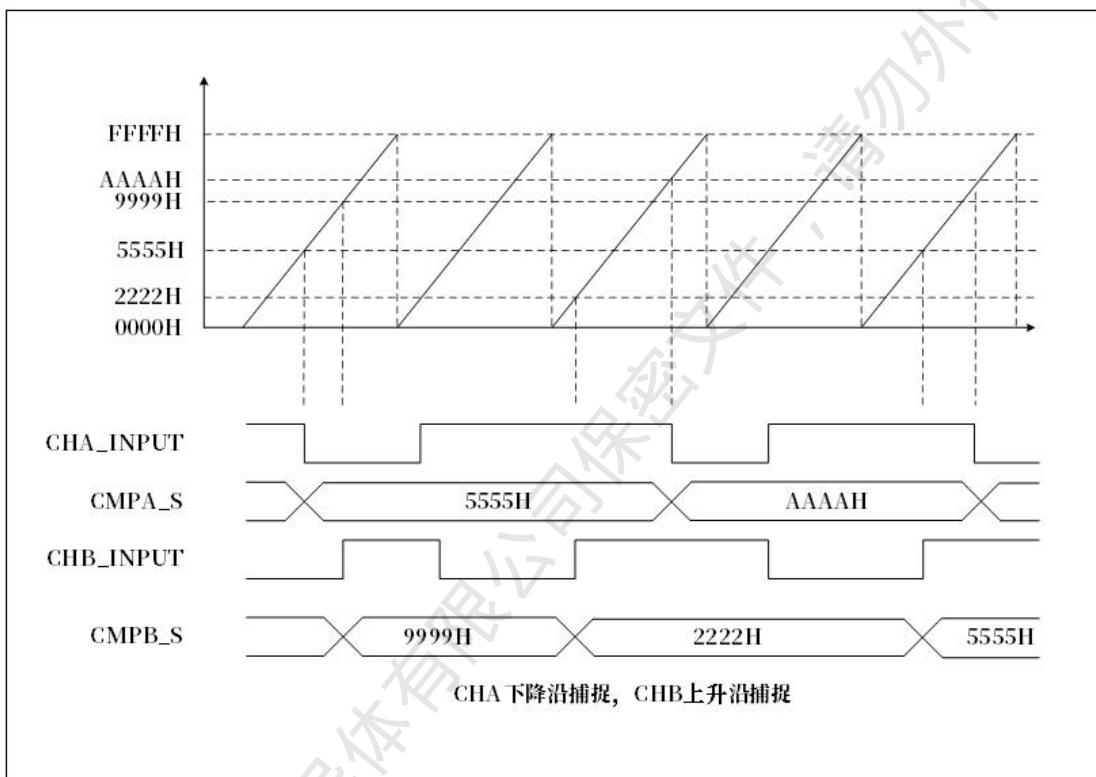

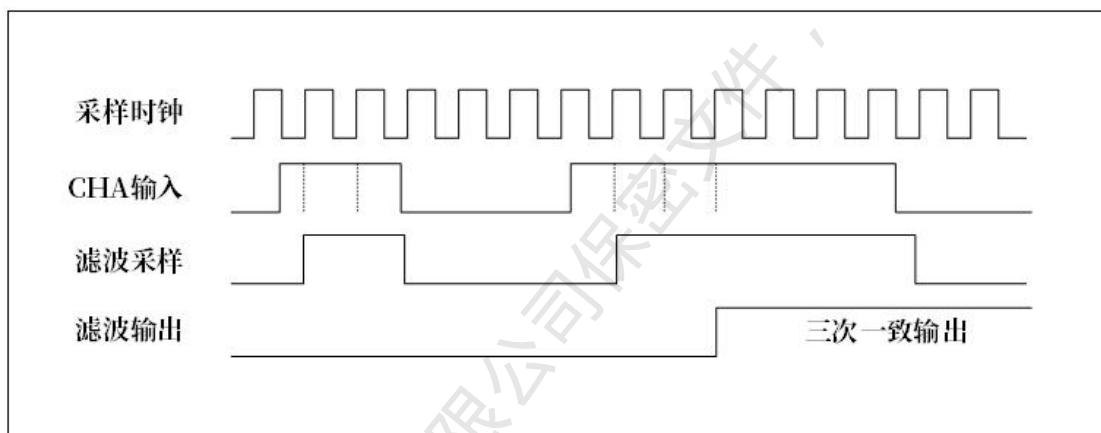

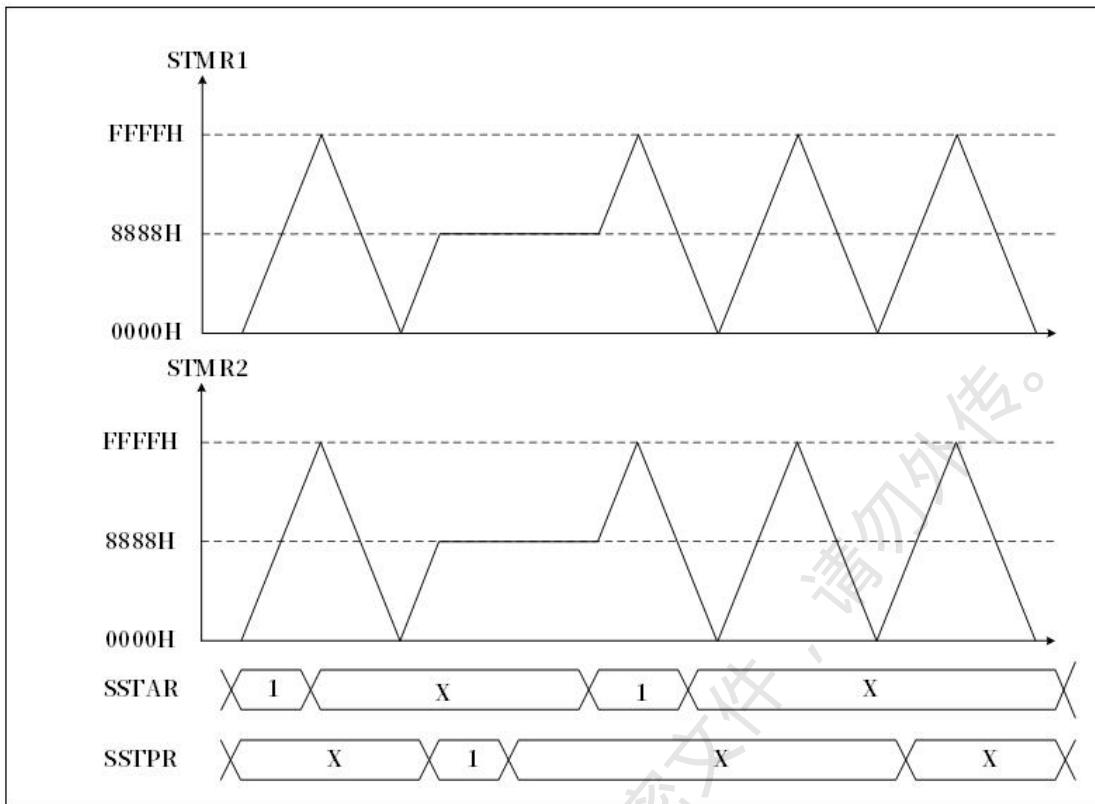

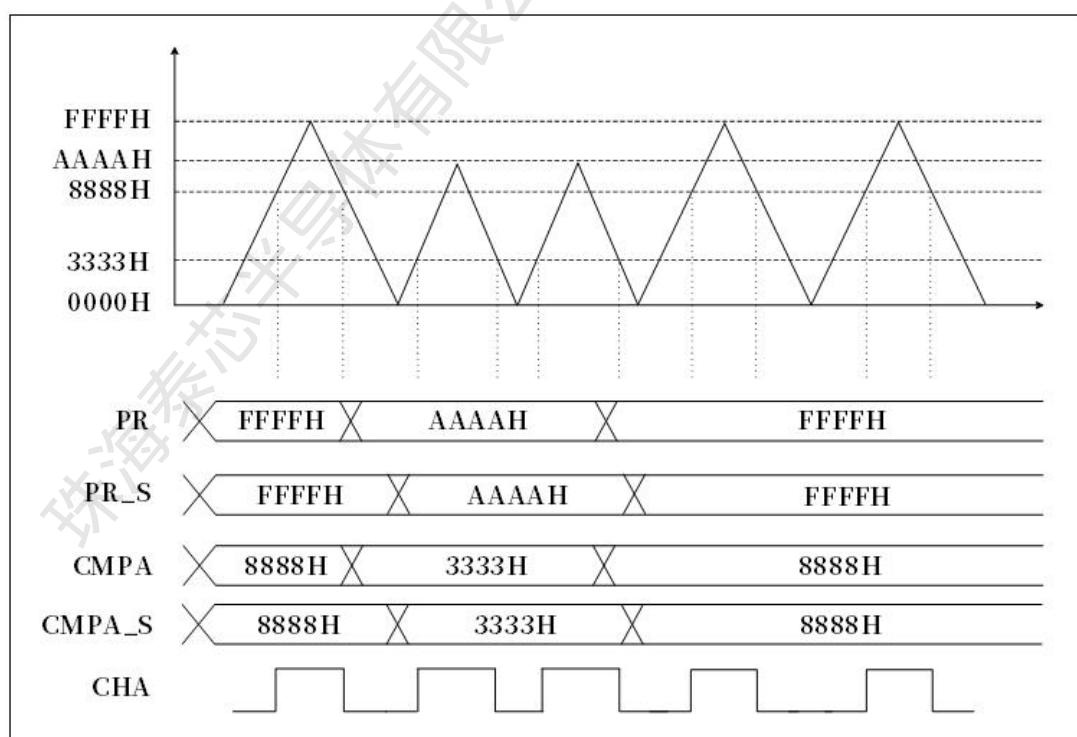

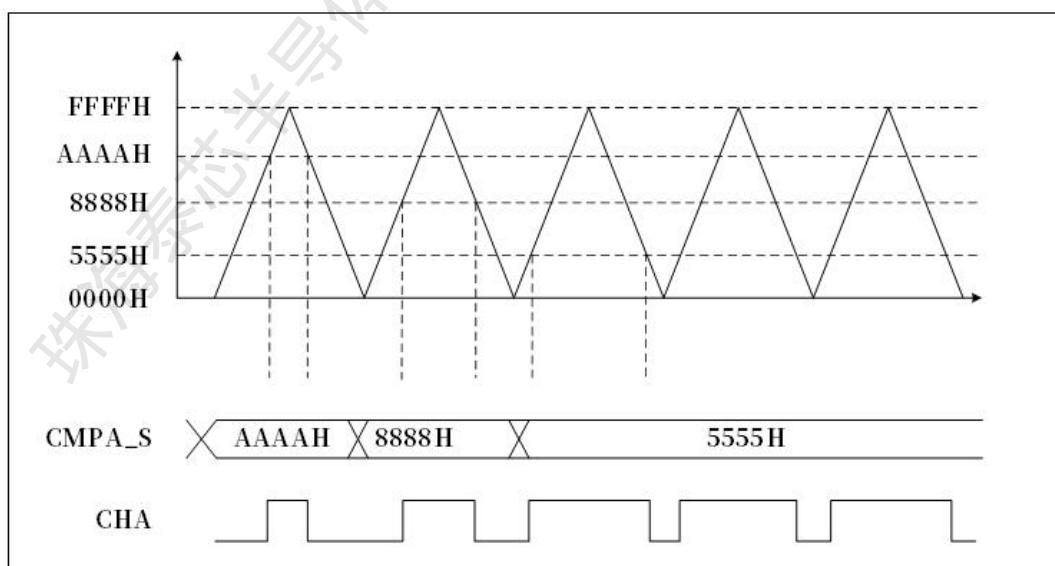

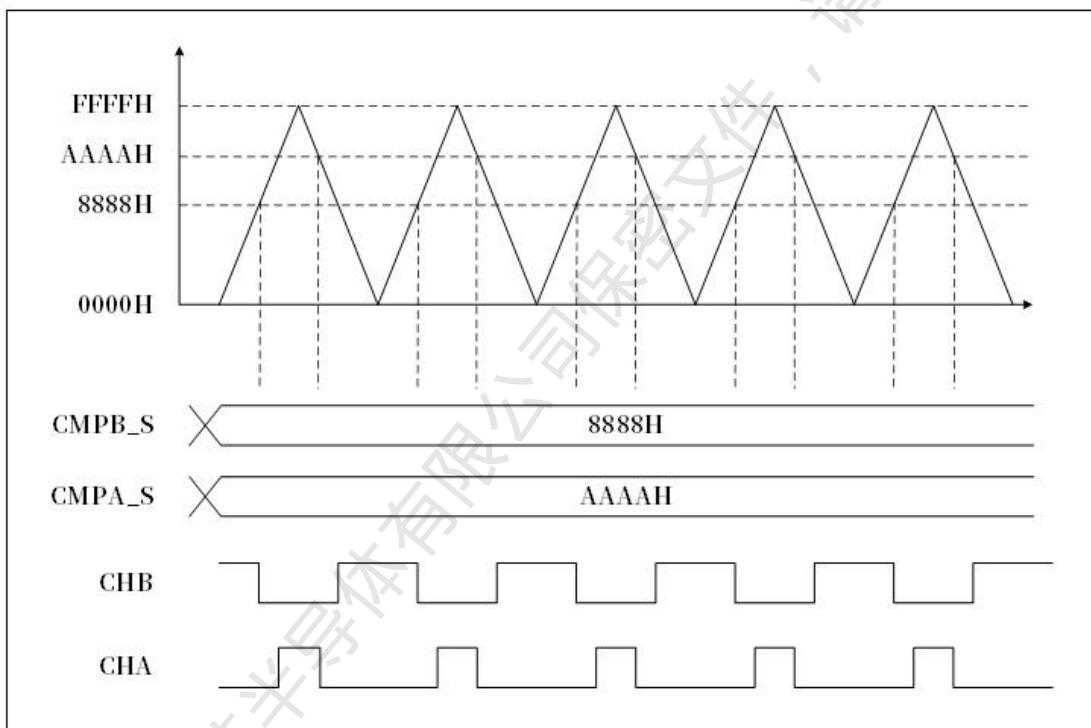

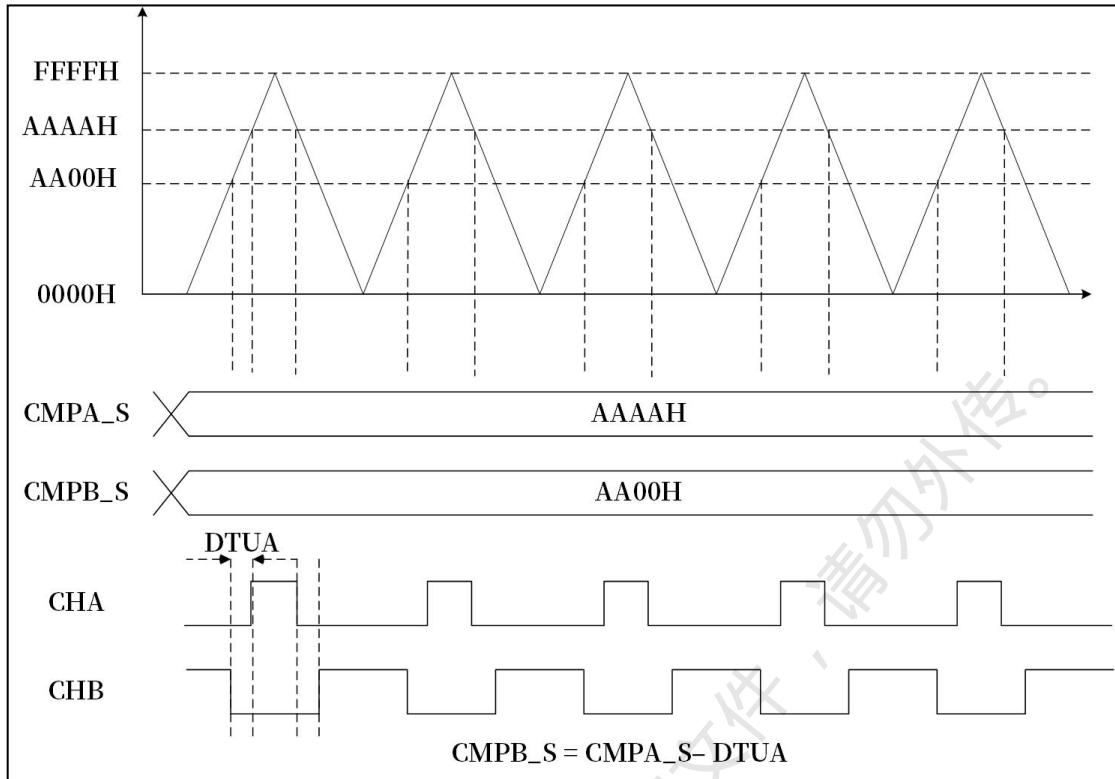

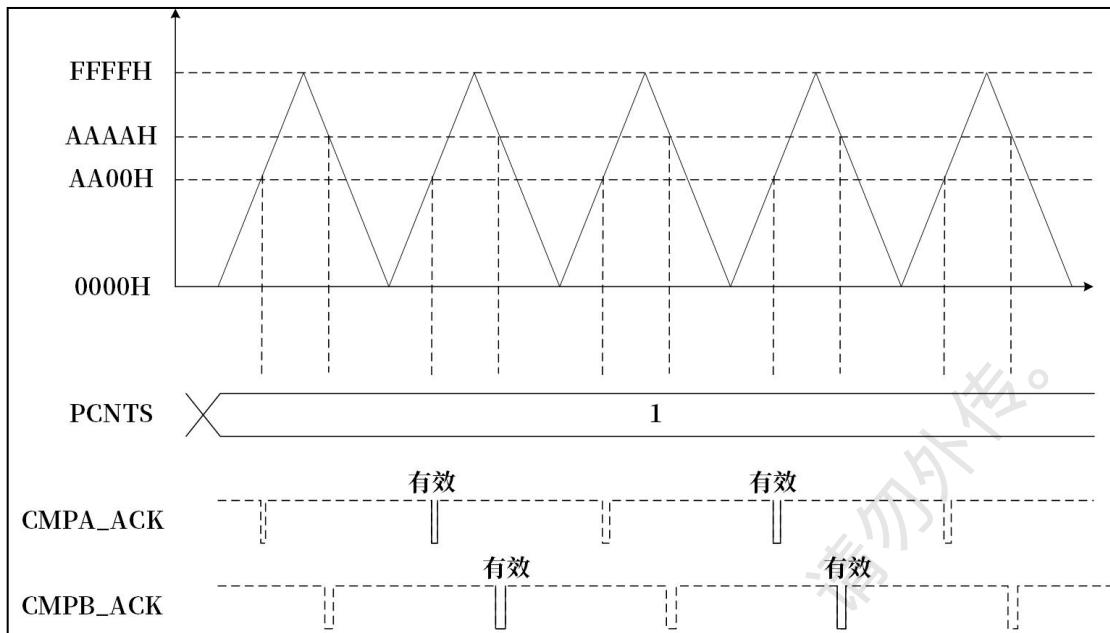

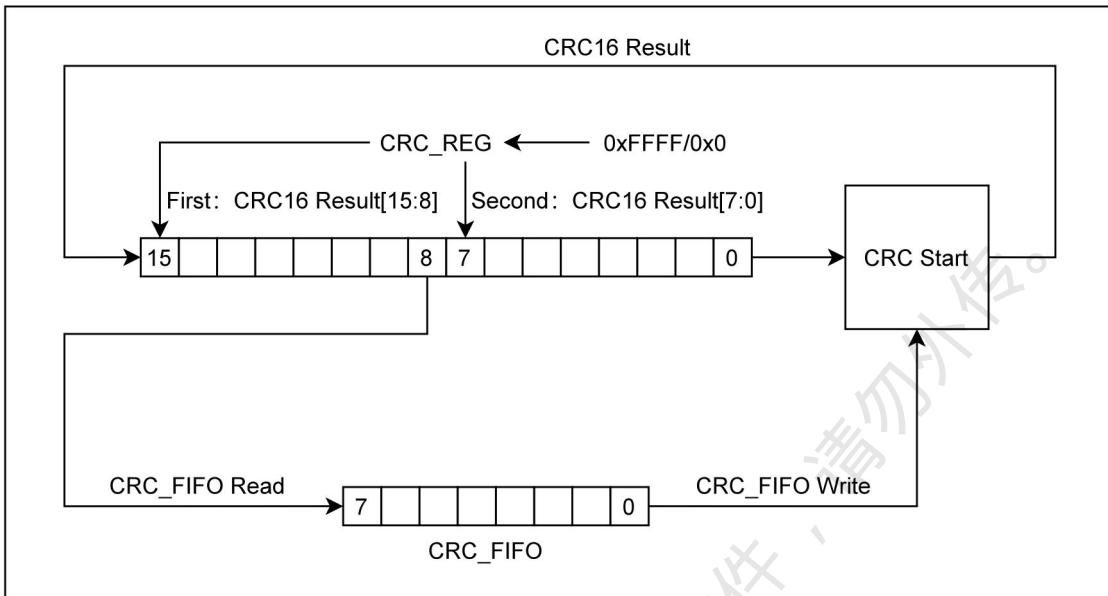

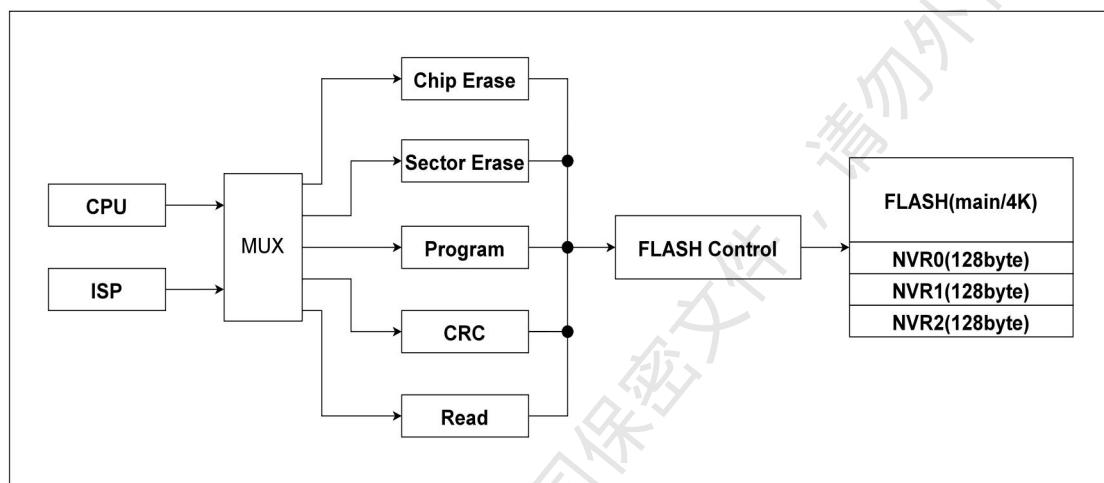

| 中断源          | 中断等级 | 中断号 | 中断地址  | 说明         |